CUDA SHARED MEMORY

shared memory��֮ǰ�IJ�����Щ���ܣ��ⲿ�ֻ�ר�Ž��������ݡ���global Memory���֣����ݶ���������Ǻ���Ҫ�Ļ��⣬��ʹ��L1��ʱ����������Ժ��ԣ����Ƿ������Ļ�ȡ�ڴ���Ȼ�ή�����ܡ��������㷨���ʣ�ijЩ����£������������Dz��ɱ���ġ�ʹ��shared memory����һ��������ܵķ�ʽ��

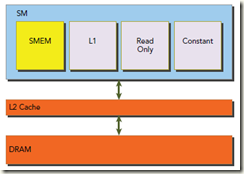

GPU�ϵ�memory�����֣�

· On-board memory

· On-chip memory

global memory����һ��ܴ��on-board memory�������кܸߵ�latency����shared memory�����෴����һ���С�����ӳٵ�on-chip memory����global memoryӵ�иߵö�Ĵ��������ǿ����������ɱ�̵�cache������Ҫ�����У�

· An intra-block thread communication channel �̼߳佻��ͨ��

· A program-managed cache for global memory data�ɱ��cache

· Scratch pad memory for transforming data to improve global memory access patterns

������Ҫ�漰�������������ͣ�reduction kernel��matrix transpose kernel��

shared memory��SMEM����GPU����Ҫ���֮һ�������ϣ�ÿ��SM����һ����ǰ����ִ�е�block������thread�����ĵ��ӳٵ��ڴ�ء�SMEMʹ��ͬһ��block�е�thread�ܹ������������on-chip���ݣ������ܹ���������kernel��Ҫ��global memory����������APP����ֱ����ʽ�IJ���SMEM�����ݣ������ֱ���Ϊ�ɱ�̻��档

����shared memory��L1Ҫ��L2��global memory���ӽ�SM��shared memory���ӳٱ�global memory��20��30����������Լ��10����

��һ��block��ʼִ��ʱ��GPU�������һ��������shared memory�����shared memory�ĵ�ַ�ռ����block�е�����thread ������shared memory�ǻ��ָ�SM��פ��������block�ģ�Ҳ��GPU��ϡȱ��Դ�����ԣ�ʹ��Խ���shared memory���ܹ����е�active��Խ�١�

����Program-Managed Cache����C���Ա���ѭ����loop transformation��һ�㶼ʹ��cache���Ż�����ѭ��������ʱ��ʹ���������еĵ���˳����Ժܺ�����cache�ֲ��ԡ����㷨�����ϣ�������Ҫ�ֶ�����ѭ�����ﵽ��������Ŀռ�ֲ��ԣ�ͬʱ��Ҫ����cache size��cache���ڳ���Ա��˵�����ģ��������ᴦ�����е������ƶ�������û����������cache����Ϊ��shared memory����һ���ɱ�̿ɲ�����cache������Ա������ȫ��������Ϊ��

Shared Memory Allocation

���ǿ��Զ�̬���߾�̬�ķ���shared Memory����������������kernel�ڲ�Ҳ������Ϊȫ�ֱ�����

���ʶ��Ϊ��__shared__��

������仰��̬��������һ��2D�ĸ��������飺

__shared__ float tile[size_y][size_x];

�����kernel�������Ļ��������������kernel�ڣ������Ƕ�����kernel��Ч�����shared Memory�Ĵ�С�ڱ�����δ֪�Ļ�������ʹ��extern�ؼ������Σ�������������һ��δ֪��С��1D���飺

extern __shared__ int tile[];

�������С�ڱ�����δ֪��������Ҫ��ÿ��kernel����ʱ����̬�ķ�����shared memory��Ҳ�����ʼ�ἰ�ĵ�����������

kernel<<<grid, block, isize * sizeof(int)>>>(...)

Ӧ��ע���ֻ��1D�������������̬ʹ�á�

Shared Memory Banks and Access Mode

֮ǰ���Ķ�latency��bandwidth���˳�����о�����shared memory�ܹ�������������latency��bandwidth�����ܵ�Ӱ�졣���潫����shared memory����֯��ʽ���Ա��о�������ܵ�Ӱ�졣

Memory Banks

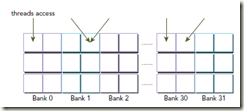

Ϊ�˻�øߴ�����shared Memory���ֳ�32����Ӧwarp�е�thread������ȴ�С���ڴ�飬���ǿ��Ա�ͬʱ���ʡ���ͬ��CC�汾��shared memory�Բ�ͬ��ģʽӳ�䵽��ͬ�Ŀ飨�Ժ���⣩�����warp����shared Memory������ÿ��bankֻ���ʲ�����һ���ڴ��ַ����ôֻ��Ҫһ���ڴ洫��Ϳ����ˣ�������Ҫ��δ��䣬��˻ή���ڴ������ʹ�á�

Bank Conflict

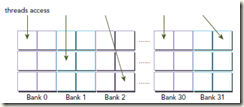

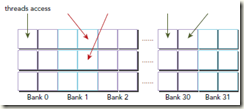

�������ַ��������ͬһ��bank�оͻᷢ��bank conflict���Ӷ�����������ִ�С�Ӳ��������������ɢ�������ܶ��û��conflict����Щ������� ���棬������Ч�����������DZ���ɢ���Ĵ������������

warp�����ֵ��͵Ļ�ȡshared memory��ģʽ��

· Parallel access�������ַ��ɢ�ڶ��bank��

· Serial access�������ַ����ͬһ��bank��

· Broadcast access��һ����ַ����������һ��bank��

Parallel access����ͨ����ģʽ�����ģʽһ�㰵ʾ��һЩ��Ҳ������ȫ������ַ�����ܹ���һ�δ���������������ǣ���ȡ��conflict��shared memory��ʱ��ÿ����ַ�������ڲ�ͬ��bank�С�

Serial access�����ģʽ�����warp�е�32��thread��������ͬһ��bank�еIJ�ͬλ�ã��Ǿ���32�ε�������������ͬʱ�����ˡ�

Broadcast accessҲ��ִֻ��һ�δ��䣬Ȼ��������㲥�����з��������thread�������Ļ��ͻᵼ�´��������ʵ͡�

��ͼ����������ķ���ͼʾ��

��ͼһ��������ʣ�ͬ��û��conflict��

��ͼ����ijЩthread���ʵ�ͬһ��bank����������������������Ϊ��

· Conflict-free broadcast access if threads access the same address within a bank

· Bank conflict access if threads access different addresses within a bank

Access Mode

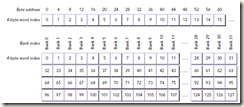

���ݲ�ͬ��CC�汾��bank������Ҳ��ͬ������Ϊ��

· 4 bytes for devices of CC 2.x

· 8 bytes for devices of CC3.x

����Fermi��һ��bank��4bytes��ÿ��bank�Ĵ�����32bitsÿ����cycle��������32λ��ӳ�䵽������bank�У�Ҳ����˵��bank��������shared memory��ַ��ӳ���ϵ���£�

bank index = (byte address ÷ 4 bytes/bank) % 32 banks

��ͼ��Fermi�ĵ�ַӳ���ϵ��ע���bank��ÿ����ַ���32�����ڵ�word�ֵ���ͬ��bank���Ա�ʹwarp�ܹ���ø���IJ��л�ȡ�ڴ��������ȡ�����ڴ�ʱ��������ַ���䵽�˲�ͬbank�У���

��ͬһ��warp������threadҪ��ȡͬһ����ַ��ע����ͬһ����ַ����ͬһ��bank����ʱ������bank conflict�����ڶ�����������һ��transaction��ý����㲥����������д����ʱ��ֻ��һ��thread������ȥд�������ĸ�threadִ����д����֪���ģ�undefined����

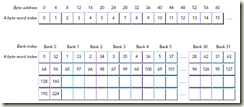

��8bytesģʽ�У�ͬ��4bytes��������64-bits�ֻ�ӳ�䵽������bank��ÿ��bank������64bite/1��clock����ӳ���ϵ��ʽ��

bank index = (byte address ÷ 8 bytes/bank) % 32 banks

����������thread����ͬһ��64-bit�е�����һ����������word��1byte��Ҳ���ᵼ��bank conflict����Ϊһ��64-bit��bank����64bit/cycle���Ķ��Ϳ������������ˡ�Ҳ����˵��ͬ������£�64-bitģʽһ���32-bitģʽ��������bank conflict��

��ͼ��64-bit�Ĺ�ϵͼ������word0��word32����bank0�У�ͬʱ��������wordҲ���ᵼ��bank conflict��64-bit/cycle����

��ͼ��64-bitģʽ�£�conflict-free�������ÿ��thread��ȡ��ͬ��bank��

��ͼ����һ��conflict-free���������thread���ȡͬһ��bank�е�word��

��ͼ��ɫ��ͷ��bank conflict�����������

Memory Padding

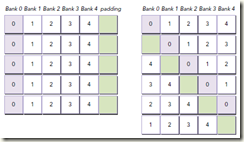

memory padding��һ�ֱ���bank conflict�ķ���������ͼ��ʾ�����е�thread�ֱ������bank0�������ͬ��word����ʱ�ͻᵼ��bank conflict�����Dz�ȡ�ķ���������ÿN��bank��Ŀ����word�����һ��word����������������ͼ������ԭ��bank0��ÿ��wordת�Ƶ��˲�ͬ��bank�У��Ӷ�������bank conflict��

���ӵ���дword���������洢���ݣ���Ψһ�����þ����ƶ�ԭʼbank�е�word��ʹ��memory padding�ᵼ��block�ɻ��shared memory�����õ��������١����о��ǣ�Ҫ���¼���������������ȡ��ȷ������Ԫ�ء�

Access Mode Configuration

��Kepler��˵��Ĭ�������4-byteģʽ�������������API���鿴��

cudaError_t cudaDeviceGetSharedMemConfig(cudaSharedMemConfig *pConfig);

���ؽ������pConfig�У������������������֣�

cudaSharedMemBankSizeFourByte

cudaSharedMemBankSizeEightByte

����ʹ�������API������bank�Ĵ�С��

cudaError_t cudaDeviceSetSharedMemConfig(cudaSharedMemConfig config);

bank�����ò����������֣�

cudaSharedMemBankSizeDefault

cudaSharedMemBankSizeFourByte

cudaSharedMemBankSizeEightByte

����������ͬ��kernel֮����bank���û���һ����ʽ��deviceͬ������shared memory��bank��С��������shared memory�����û���Ӱ��kernel��Occupancy�����Ƕ�������һ����Ҫ��Ӱ�����ء�һ�����bank������ϸߵĴ��������Ǽ��ڲ�ͬ��access pattern�����ܵ��¸����bank conflict��

Synchronization

��Ϊshared Memory���Ա�ͬһ��block�еIJ�ͬ��threadͬʱ���ʣ���ͬһ����ַ��ֵ�����thread�ľ͵�����inter-thread conflict������������Ҫͬ��������CUDA�ṩ������block�ڲ���ͬ������������

· Barriers

· Memory fences

����barrier������thread��ȴ�����thread����barrier point������Memory fence������thread��������������Memory�IJ���������thread�ɼ������������CUDA��Ҫͬ������Ҫԭ��weakly-ordered��

Weakly-Ordered Memory Model

�ִ��ڴ�ܹ��зdz����ɵ��ڴ�ģʽ��Ҳ������ζ�ţ�Memory�Ļ�ȡ���ذ��ճ����е�˳����ִ�С�CUDA������һ�ֽ���weakly-ordered Memory model����ȡ�������ı������Ż���

GPU threadд���ݵ���ͬ��Memory��˳����shared Memory��global Memory��page-locked host memory������һ��device�ϵ�Memory��ͬ��û��Ҫ����������˳������ͬ��һ��thread�Ķ�������˳�������thread�ɼ�ʱҲ������ʵ����ִ��д������thread˳��һ�¡�

Ϊ����ʽ��ǿ�Ƴ�����һ��ȷ�е�˳�����У�����Ҫ�õ�fence��barrier������Ҳ��Ψһ�ܱ�֤kernel��Memory����ȷ����Ϊ�IJ�����

Explicit Barrier

ͬ������������֮ǰ��������Ҳ�ᵽ�����٣��������������

void __syncthreads();

__syncthreads������Ϊһ��barrier point�����ã�block�е�thread����ȴ�����thread���������point����ܼ�����һ������Ҳ��֤�����������point֮ǰ��ȡglobal Memory��shared Memory�IJ�����ͬһ��block������thread�ɼ���__syncthreads������Э��ͬһ��block�е�thread����һЩthread��ȡMemory��ͬ�ĵ�ַʱ���ͻᵼ��DZ�ڵ����⣨����д��д�����д��д���Ӷ�����δ������Ϊ״̬����ʱ�Ϳ���ʹ��__syncthreads���������������

ʹ��__syncthreadsҪ�൱С�ģ�ֻ��������thread���ᵽ�����pointʱ�ſ��Ե������ͬ�����Զ��������ͬһ��block�е�ijЩthread��Զ������õ㣬��ô����һֱ����ȥ������������һ�ִ����ʹ�÷�ʽ��

if (threadID % 2 == 0) { __syncthreads(); } else { __syncthreads();}

Memory Fence

���ַ�ʽ��֤���κ���fence֮ǰ��Memoryд������fence֮��thread���ɼ���Ҳ���ǣ�fence֮ǰд���ˣ�fence֮������thread�Ͷ�֪�����Memoryд���ֵ�ˡ�fence�����÷�Χ�ȽϹ㣬��Ϊ��block��grid��system��

����ͨ�������API������fence��

void __threadfence_block();

�����־�֪������������Ƕ�Ӧ��block��Χ��Ҳ���DZ�֤ͬһ��block��thread��fence֮ǰд���ֵ��block��������thread�ɼ�����ͬ��barrier����function����Ҫ���е�thread��ִ�С�

������grid��Χ��API������ͬ��block��Χ���������block����grid�����ˣ�

void __threadfence();

������system�ģ��䷶Χ�������ϵͳ������device��host��

void __threadfence_system();

Volatile Oualifier

����һ��ʹ��global Memory����shared Memory�ı�������volatile���η������θñ����Ļ�������֯��������һ���ñ�����cache���Ż���ʹ�ø����η��������ͻ���Ϊ�ñ���������ijһʱ�̱����thread�ı䣬���ʹ��cache�Ż��Ļ����õ���ֵ��ȱ��ʱЧ�����ʹ��volatileǿ��ÿ�ζ���global ����shared Memory��ȥ��ȡ�������Чֵ��

CHECKING THE DATA LAYOUT OF SHARED MEMORY

�ò��ֻ�����һЩʹ��shared Memory�����ӣ��������¼������棺

· ����vs��������

· Row-major vs column-major access

· ��̬vs��̬shared Memory����

· ȫ��vs�ֲ�shared Memory

· Memory padding vs no Memory padding

���������ʹ��shared Memory��ʱ��Ӧ�ù�ע�������Ϣ��

· Mapping data elements across Memory banks

· Mapping from thread index to shared Memory offset

�����������㣬�Ϳ�������shared Memory��ʹ���ˣ��Ӷ�������ţ�ƵĴ��롣

Square Shared Memory

��ͼչʾ��һ��ÿһά����32��Ԫ�ز���row-major�洢��shared Memory��ͼ�����Ϸ��Ǹþ���ʵ�ʵ�һά�洢ͼʾ���·������Ķ�άshared Memory��

���ǿ���ʹ���������侲̬����һ��2D��shared Memory������

__shared__ int tile[N][N];

����ʹ������ķ�ʽ�����ݣ����ڵ�thread��ȡ���ڵ�word��

tile[threadIdx.y][threadIdx.x]

tile[threadIdx.x][threadIdx.y]

�������ַ�ʽ�ĸ������أ������Ҫע��thread��bank��ӳ���ϵ�ˣ�������ϣ���������ǣ�ͬһ��warp�е�thread��ȡ���Dz�ͬ��bank��ͬһ��warp�е�thread����ʹ��������threadIdx.x��ȷ������ͬbank�е�Ԫ��ͬ���������洢�ģ���word��С��Ϊƫ�ơ���˴Σ��������������thread����������threadIdx.xȷ������ȡshared Memory�������ĵ�ַ���ɴ˵�֪��

tile[threadIdx.y][threadIdx.x]Ӧ��չ�ֳ����õ������Լ����ٵ�bank conflict��

Accessing Row-Major versus Column-Major

�������ǵ�grid��2D��block��32,32�����������£�

#define BDIMX 32#define BDIMY 32dim3 block(BDIMX,BDIMY);dim3 grid(1,1);

���Ƕ����kernel����������������

· ��thread������row-majorд��2D��shared Memory�����С�

· ��shared Memory�ж�ȡ��Щֵ��д�뵽global Memory�С�

kernel���룺

__global__ void setRowReadRow(int *out) { // static shared memory __shared__ int tile[BDIMY][BDIMX]; // ��Ϊblockֻ��һ�� unsigned int idx = threadIdx.y * blockDim.x + threadIdx.x; // shared memory store operation tile[threadIdx.y][threadIdx.x] = idx; // ����ͬ����Ϊ��ʹ����shared Memory�Ļ�ȡ��row-majorִ�� //���е��߳�δ��ɣ��������߳��Ѿ��ڶ�shared Memory������ __syncthreads(); // shared memory load operation out[idx] = tile[threadIdx.y][threadIdx.x] ;}

�۲�����֪�������������ڴ������

· ��shared Memory������

· ��shared Memorȡ����

· ��global Memory������

��Ϊ��ͬһ��warp�е�threadʹ��������threadIdx.x������title����kernel��û��bank conflict�ġ����������������threadIdx.y��threadIdx.x��λ�ã��ͱ����column-major��˳��ÿ��shared Memory�Ķ�д���ᵼ��Fermi��32-way��bank conflict������Kepler��16-way��bank conflict��

__global__ void setColReadCol(int *out) { // static shared memor __shared__ int tile[BDIMX][BDIMY]; // mapping from thread index to global memory index unsigned int idx = threadIdx.y * blockDim.x + threadIdx.x; // shared memory store operation tile[threadIdx.x][threadIdx.y] = idx; // wait for all threads to complete __syncthreads(); // shared memory load operation out[idx] = tile[threadIdx.x][threadIdx.y];}

��������

$ nvcc checkSmemSquare.cu –o smemSquare$ nvprof ./smemSquare��Tesla K40c��4-byteģʽ���ϵĽ�����£�������������ģ�row-major����Ҫ��ɫ��

./smemSquare at device 0 of Tesla K40c with Bank Mode:4-byte<<< grid (1,1) block (32,32)>>Time(%) Time Calls Avg Min Max Name13.25% 2.6880us 1 2.6880us 2.6880us 2.6880us setColReadCol(int*)11.36% 2.3040us 1 2.3040us 2.3040us 2.3040us setRowReadRow(int*)

Ȼ��ʹ��nvprof�����������������������Ӧ��bank-conflict��

shared_load_transactions_per_request

shared_store_transactions_per_request

������£�row-majorֻ��һ��transaction��

Kernel:setColReadCol (int*)1 shared_load_transactions_per_request 16.0000001 shared_store_transactions_per_request 16.000000Kernel:setRowReadRow(int*)1 shared_load_transactions_per_request 1.0000001 shared_store_transactions_per_request 1.000000Writing Row-Major and Reading Column-Major

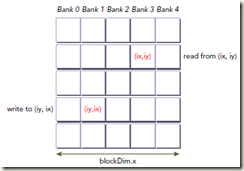

���ڵ�kernelʵ����row-majorдshared Memory����Column-major��shared Memory����ͼָ���������ֲ�����ʵ�֣�

kernel���룺

__global__ void setRowReadCol(int *out) { // static shared memory __shared__ int tile[BDIMY][BDIMX]; // mapping from thread index to global memory index unsigned int idx = threadIdx.y * blockDim.x + threadIdx.x; // shared memory store operation tile[threadIdx.y][threadIdx.x] = idx; // wait for all threads to complete __syncthreads(); // shared memory load operation out[idx] = tile[threadIdx.x][threadIdx.y];}

�鿴nvprof�����

Kernel:setRowReadCol (int*)1 shared_load_transactions_per_request 16.0000001 shared_store_transactions_per_request 1.000000

д������û��conflict�ģ���������������һ��16�ε�transaction��

Dynamic Shared Memory

����ǰ����˵�����ǿ���ȫ�ַ�Χ�Ķ�̬����shared Memory��Ҳ������kernel�ڲ���̬����һ���ֲ���Χ��shared Memory��ע�⣬��̬����������δȷ����Сһά���飬��ˣ����Ǿ���Ҫ���¼�����������Ϊ���ǽ�Ҫ��row-majorд����colu-major�������Ծ���Ҫ����������������ֵ��

· row_idx��1D row-major �ڴ��ƫ��

· col_idx��1D column-major�ڴ�ƫ��

kernel���룺

__global__ void setRowReadColDyn(int *out) { // dynamic shared memory extern __shared__ int tile[]; // mapping from thread index to global memory index unsigned int row_idx = threadIdx.y * blockDim.x + threadIdx.x; unsigned int col_idx = threadIdx.x * blockDim.y + threadIdx.y; // shared memory store operation tile[row_idx] = row_idx; // wait for all threads to complete __syncthreads(); // shared memory load operation out[row_idx] = tile[col_idx];}

kernel����ʱ���õ�shared Memory��

setRowReadColDyn<<<grid, block, BDIMX * BDIMY * sizeof(int)>>>(d_C);

�鿴transaction��

Kernel: setRowReadColDyn(int*)1 shared_load_transactions_per_request 16.0000001 shared_store_transactions_per_request 1.000000

�ý����֮ǰ��������ͬ����������ʹ�õ��Ƕ�̬������

Padding Statically Declared Shared Memory

ֱ�ӿ�kernel���룺

__global__ void setRowReadColPad(int *out) { // static shared memory __shared__ int tile[BDIMY][BDIMX+IPAD]; // mapping from thread index to global memory offset unsigned int idx = threadIdx.y * blockDim.x + threadIdx.x; // shared memory store operation tile[threadIdx.y][threadIdx.x] = idx; // wait for all threads to complete __syncthreads(); // shared memory load operation out[idx] = tile[threadIdx.x][threadIdx.y];}

�Ĵ�����setRowReadCol�ķ��棬�鿴�����

Kernel: setRowReadColPad(int*)1 shared_load_transactions_per_request 1.0000001 shared_store_transactions_per_request 1.000000

����������������load��bank_conflict�Ѿ���ʧ����Fermi�ϣ�ֻ��Ҫ����һ�оͿ��Խ��bank-conflict��������Kepler��ȴ��һ������ȡ����2D shared Memory�Ĵ�С����˶���8-byteģʽ��������Ҫ���������ܵõ���ȷ�����

�ο��顶professional cuda c programming��