目录

- always--------------过程赋值语句

-

- 1.输出类型reg

- 2.时序和组合

- 3.always @(*)

-

- (1)避免latch的方法

- 4.always @(posedge clk)

- 5.非阻塞赋值

- assign----------------连续赋值语句

-

- 1.输出类型wire

- 2.阻塞赋值

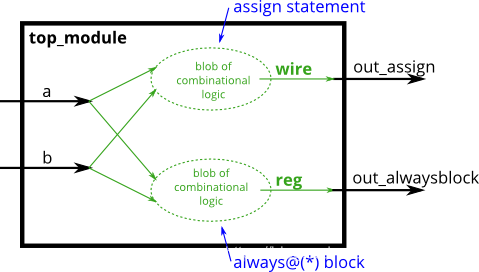

- 以下为对比图

always--------------过程赋值语句

1.输出类型reg

(1)always内部输出一般使用reg类型

(2)reg在组合电路中和wire其实类似,在时序电路中为触发器样式

2.时序和组合

//组合逻辑

always @(*)

//时序逻辑

always @(posedge xx)

3.always @(*)

此时类似组合逻辑,只有当块内发生变化,那么才会执行

和assign类似,以下代码其实并不会实行,因为a赋值为1’b1只有在a发生变化的时候执行。也就是此时我们并不知道a的值是多少。

always @(*)begina = 1'b1;

end

使用always @(*)来进行组合逻辑的时候一定要注意避免产生latch

也就是always内部有if但是没有else,这样就会导致只在if的时候对某个值进行了赋值,但是当if不执行的时候,某个值就会没有确切的值导致了latch的产生,这是非常危险的。同时对于case没有default也会产生latch

(1)避免latch的方法

在任何要对输出进行判断赋值之前先赋初始值

4.always @(posedge clk)

此时加上了触发条件,为触发器

以下代码则会在每一个上升沿给a赋值为1'b1

always @(posedge clk)begina <= 1'b1;

end

5.非阻塞赋值

//以下执行为a = 1,b = 0,然后第二个clk才是a = 1,b = 1,

//也就是a<= 1和b<= a同时执行

initial begina = 1'b0;b = 1'b1;

end

always @(posedge clk)begina <= 1;b <= a;

end

assign----------------连续赋值语句

1.输出类型wire

(1)assign输出的wire就像一根连线可以进行后续连接,一般用在不同module的连接上

(2)assign内部不能实现复杂逻辑

(3)module实例化的时候必须使用wire

(4)要明确wire就是一根线

2.阻塞赋值

//执行后a = 1,b = 1,也就是只有在a = 1执行后b = a才会执行

always @(*)begina = 1;b = a;

end

以下为对比图