ЧАМИЦЊВЉЮФЬсЕНСЫЫФжжЪБађТЗОЖЃКЛљБОЕФЪБађдМЪјЁЂЗжЮіЕФИХФю

1) FPGAФкВПЪБађЕЅдЊМфЕФТЗОЖ

2) ЪфШыЖЫПкЕНFPGAФкВПЪБађЕЅдЊЕФТЗОЖ

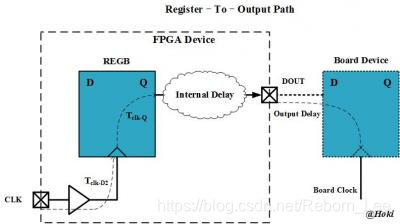

3) FPGAФкВПЪБађЕЅдЊЕНЪфГіЖЫПкЕФТЗОЖ

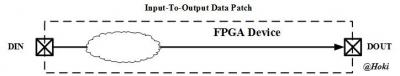

4) ЪфШыЖЫПкЕНЪфГіЖЫПкЕФТЗОЖ

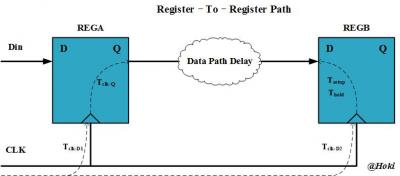

Цфжа1. FPGAФкВПЪБађЕЅдЊМфЕФТЗОЖжаЃЌЪБађЗжЮіЫљашвЊЕФЪБМфВЮЪ§ЃКTclk-D1, Tclk-Q, Tdata_path_delay, Tclk_D2, Tsetup, TholdвбФмШЗЖЈЃЌжЛвЊЪєгкFPGAФкВПЕФЪБМфВЮЪ§ЃЌVivadoдђЛсИљОнЯргІЩшМЦМЦЫуЕУЕНЃЌвђДЫ4. ЪфШыЖЫПкЕНЪфГіЖЫПкЕФТЗОЖЕФЪБМфВЮЪ§вВФмШЗЖЈЁЃ

ЦфЫќСНЬѕТЗОЖЖМЯргІШБЩйFPGAЭтВПЕФМИИіЪБМфВЮЪ§ЃЌетаЉВЮЪ§ЖМашвЊЭЈЙ§ЪБађдМЪјИцжЊVivadoЃЌШЛКѓVivadoВХФмОЋШЗЕиНјааетаЉТЗОЖЕФЪБађЗжЮіЁЃетвЛНкЯШНщЩм

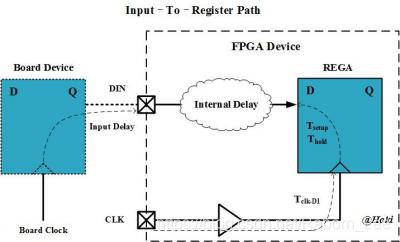

2. ЪфШыЖЫПкЕНFPGAФкВПЪБађЕЅдЊЕФТЗОЖетЬѕТЗОЖЕФдМЪјЁЃ

дкЪфШыЖЫПкЕНFPGAФкВПЪБађЕЅдЊЕФТЗОЖжаЃЌInput DelayетЖЮТЗОЖЪЧдкFPGAЭтВПЃЌвђДЫашвЊдМЪјЩшжУЦфЪБМфВЮЪ§ЃЌЭЈЙ§set_input_delayдМЪјУќСюдМЪјЃЌОпЬхШчЯТЃК

set_input_delay ЈCclock{clk} ЈCmax/-min input_delay_value [get_ports {DIN}]

СэЭтИљОнsource clockКЭdestination clockЃЌЪфШыНгПкПЩЗжЮЊвдЯТСНжжЧщПіЃК

System Synchronous Input

ЗжЮіЪфШыЖЫПкЕНFPGAФкВПЪБађЕЅдЊЕФТЗОЖЪБЃЌЕБsource clockКЭdestination clockРДздЭЌвЛИіЯЕЭГЪБжгЪБЃЌГЦЮЊЯЕЭГЭЌВНЪфШы(system synchronous input)ЁЃ

ШчЭМ1ЫљЪОЮЊЯЕЭГЭЌВНЪфШыЃЌsource clockЪЧCLKAЃЌdestination clockЪЧCLKBЃЌЦфжаCLKBЭЈЙ§ЪфШыЖЫПкв§ШыFPGAФкВП(дМЪјГЩжїЪБжг)ЃЌЖјCLKAв§ЕНСЫFPGAЭтВПЕФАхЩЯаОЦЌЃЌВЂУЛгав§ШыЕНFPGAФкВПЃЌCLKBЪЧВЩМЏЪфШыЖЫПкЕФЪБжгЃЌвђДЫЪзЯШдМЪјCLKBЮЊжїЪБжгЃЌдМЪјШчЯТЃК

create_clock -name CLKB -period 10 -waveform {0 5} [get_ports {CLKB}]

ЃЈЭМ1ЃЉ

ЦфжаTclkd_extБэЪОЭтВПЪБжгдДЕНЭтВПаОЦЌЕФбгЪБЃЛTclkd_intБэЪОЭтВПЪБжгдДЕНFPGAЪфШыЖЫПкЕФбгЪБЃЛTcoБэЪОЭтВПаОЦЌtCOЪБМфЃЛTbdБэЪОЭтВПаОЦЌЪфГіЖЫПкЕНFPGAаОЦЌЕФАхЩЯбгЪБЁЃ

ЖдгІmax_input_delayКЭmin_input_delayЃЌвдЩЯМИИіЪБМфВЮЪ§ЖМгаmaxКЭminжЕЃЌдМЪјШчЯТЃК

set_input_delay -clock CLKB -max [Tclkd_ext_max + Tco_max + Tbd_max ЈC Tclkd_int_min] [ get_ports DIN ]

set_input_delay -clock CLKB -min [Tclkd_ext_min + Tco_min + Tbd_min ЈC Tclkd_int_max] [ get_ports DIN ]

Source Synchronous Input

ЗжЮіЪфШыЖЫПкЕНFPGAФкВПЪБађЕЅдЊЕФТЗОЖЪБЃЌЕБdestination clockРДздЭтВПаОЦЌЃЌМДгыЪ§ОнЪфШыЭЌдДЃЌГЦЮЊдДЭЌВНЪфШы(source synchronous input)ЁЃ

НсЙЙШчЭМ2ЫљЪОЃЌДгАхЩЯаОЦЌЪфШыЕНFPGAГ§СЫгаЪ§ОнЃЌЛЙгавЛИіЫцТЗЪБжгЃЌЪЧгЩАхЩЯаОЦЌВњЩњЕФЁЃ

ЃЈЭМ2ЃЉ

???????Input Delay ValueЃК

дМЪјInput DelayЗжmaxжЕКЭminжЕЃЌВЮПМЭМ2жаЪБМфВЮЪ§ЃЌЦфжаTcdБэЪОЭтВПаОЦЌЪБжгЪфГіЕНFPGAЪфШыЖЫПкЕФбгЪБЃЛTcoБэЪОЭтВПаОЦЌtCOЪБМфЃЛTbdБэЪОЭтВПаОЦЌЪфГіЖЫПкЕНFPGAаОЦЌЕФАхЩЯбгЪБЁЃInput delayЕФМЦЫуЪНШчЯТЃК

max_input_delay = Tbd_max + Tco_max - Tcd_min

min_input_delay = Tbd_min + Tco_min - Tcd_max

???????Clock & DataЃК

дДЭЌВНЪфШыЕФдМЪјЯрБШгкЯЕЭГЭЌВНЪфШыЕФИДдгаЉЃЌЦфИљОнЪБжггыЪ§ОнЕФЙиЯЕЃЌПЩЗжЮЊБпдЕЖдЦы(Edge Aligned Clock&Data)КЭжааФЖдЦы(Center Aligned Clock&Data)СНжжЃК

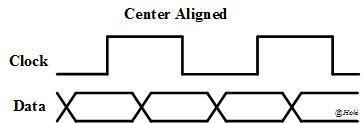

1) Center Aligned

жааФЖдЦыЪЧжИЪБжгКЭЪ§ОнЕНДяКѓМЖЪБађЕЅдЊЪБЃЌЪБжгбидкЪ§ОнжааФЃЌШчЭМ3ЫљЪОЁЃ

дкетжжЧщПіЯТПЩвджБНгЪЙгУЪБжгВЩМЏЪ§ОнЁЃ

ЃЈЭМ3ЃЉ

дМЪјШчЯТЃК

create_clock -name CLKB -period clk_period [get_ports {CLKB}]

set_input_delay -clock[get_clocks CLKB] -max max_input_delay [get_ports indata]

set_input_delay -clock[get_clocks CLKB] -min min_input_delay [get_ports indata] -add_delay

2) Edge Aligned

БпдЕЖдЦыЪЧжИЪБжгКЭЪ§ОнЕНДяКѓМЖЪБађЕЅдЊЪБЃЌЪБжгбигыЪ§ОнБфЛЏбижиКЯЃЌШчЭМ4ЫљЪОЁЃ

ЃЈЭМ4ЃЉ

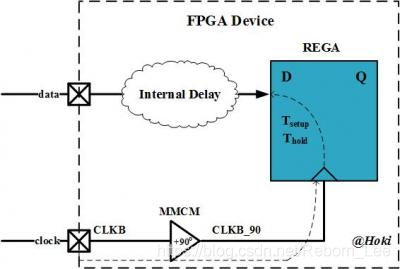

етжжЧщПіЯТЯдШЛВЛТњзуКѓМЖЪБађЕЅдЊЕФSetupвЊЧѓЃЌвђДЫЪБжгашвЊОЙ§вЛЖЈЕФвЦЯрВХФмШЅВЩМЏЪ§ОнЃЌЭЈГЃВЩгУMMCMФЃПщЪЕЯжвЦЯрЃЌШчЭМ5ЫљЪОЁЃ

ЭМЃЈ5ЃЉ

ЪБжгдМЪјШчЯТЃК

create_clock -name CLKB -period clk_period [get_ports {CLKB}]

create_generated_clock -name CLKB_90 -source [get_clocks CLKB] ЈCphase 90 [get_pins{MMCM|co[0]}]

set_input_delay -clock[get_clocks CLKB_90] -max max_input_delay [get_ports indata]

set_input_delay -clock[get_clocks CLKB_90] -min min_input_delay [get_ports indata] -add_delay

SDR & DDRЃК

дДЭЌВННгПкГЃгУгкИпЫйЪ§ОнДЋЪфЃЌШчDDRДцДЂЦїЁЂHyperTransportзмЯпКЭSPI-4.2БъзМНгПкЕШЁЃЦфжаDDRжИЫЋБЖЫйТЪЪ§ОнВЩМЏ(Double Data Rate)ЃЌдкЪБжгЕФЩЯЩ§биКЭЯТНЕбиЖМДЋЪфЪ§ОнЪЕЯжЫЋБЖЫйТЪЁЃ

1) SDR(Single Data Rate)

ЕЅБЖЫйТЪЪ§ОнВЩМЏжЛдкЪБжгЕФЩЯЩ§биЛђепЯТНЕбиВЩМЏЪ§ОнЃЌШчЭМ6ЫљЪОЁЃ

ЭМ6

InputдМЪјжЛашеыЖдЪБжгЕФЩЯЩ§биЛђепЯТНЕбиНјааЃЌШчЃК

set_input_delay -clock[get_clocks CLKB] -max max_input_delay [get_ports indata]

set_input_delay -clock[get_clocks CLKB] -min min_input_delay [get_ports indata] -add_delay

2) DDR(Double Data Rate)

ЫЋБЖЫйТЪЪ§ОнВЩМЏдкЪБжгЕФЩЯЩ§биКЭЯТНЕбиЖМВЩМЏЪ§ОнЃЌШчЭМ7ЫљЪОЁЃ

ЃЈЭМ7ЃЉ

еыЖдЪБжгЕФЩЯЩ§биКЭЯТНЕбиЖМашвЊНјааInputдМЪјЃЌШчЃК

set_input_delay -clock[get_clocks CLKB] -max max_input_delay [get_ports indata]

set_input_delay -clock[get_clocks CLKB] -min min_input_delay [get_ports indata] -add_delay

set_input_delay -clock[get_clocks CLKB] -max max_input_delay [get_ports indata] -clock_fall -add_delay

set_input_delay -clock[get_clocks CLKB] -min min_input_delay [get_ports indata] -clock_fall -add_delay

???????Timing Check in Vivado

вдЩЯНВНтСЫШчКЮНјааInput delayЕФдМЪјЃЌПЩФмДѓМвЛЙВЛУїАзЮЊЪВУДашвЊдМЪјinput delay?ФЧЯТУцОЭНВНтвЛЯТinput delay дкЪБађЗжЮіжаЕФзїгУЃК

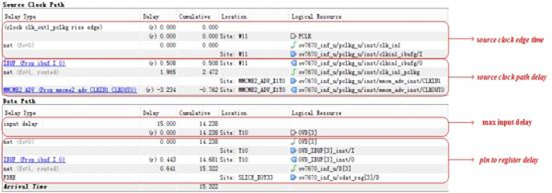

дкVivadoжаЪБађЗжЮіЗжЮЊsetup checkКЭhold checkЃЌЦфжав§ШыСЫsetup slackКЭhold slackРДНчЖЈЪБађЪЧЗёЪеСВЁЃдкЁЖ2. Timing BasicsЁЗжаНщЩмЙ§FPGAФкВПregister_to_registerТЗОЖsetup slackКЭhold slackЕФМЦЫуЗНЗЈЃЌБОЮФдђНщЩмвЛЯТЪфШыЖЫПкЕНFPGAФкВПЪБађЕЅдЊЕФТЗОЖslackЕФМЦЫуЗНЗЈЃЌЙЋЪНШчЯТЃК

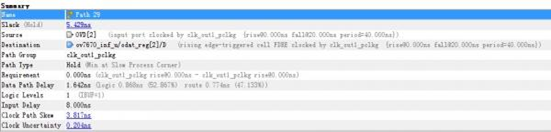

Setup check:

setup slack = data required time ЈC data arrival time

Цфжа:

data required time = destination clock edge time + destination clock path delay

- clock uncertainty

- setup time

data arrival time = source clock edge time + source clock path delay

+ max input delay

+ pin to register delay

ЮЊСЫШЗШЯЙЋЪНЕФе§ШЗадЃЌДђПЊVivadoШэМўЃЌаТНЈСЫвЛИідМЪјСЫinput delayЕФЙЄГЬЃЌШчЯТМИЭМЫљЪОЮЊжаЦфжавЛЬѕТЗОЖЕФsetup checkБЈИцЁЃ

дМЪјЕФЪБжгжмЦкЮЊ40nsЃЌmax input delayЮЊ15ns

data arrival time= 15.322ns

data required time = 40.199ns

ЪБађБЈИцжаslackМЦЫуЗНЪНгыЙЋЪНЭъШЋвЛжТЃЌвђДЫПЩвдЕУЕНsetup slack = data required time ЈC data arrival time= 40.199ns ЈC 15.322ns = 24.846nsЁЃ

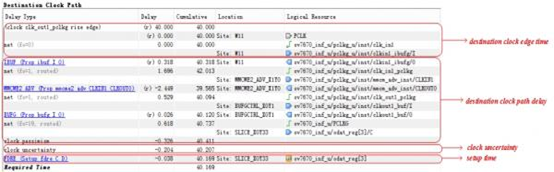

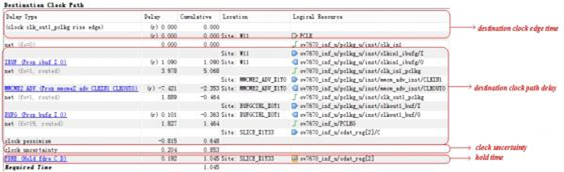

Hold check:

hold slack = data arrival time ЈC data required time

Цфжа

data required time = destination clock edge time + destination clock path delay

+ clock uncertainty

+ hold time

data arrival time = source edge time + source clock path delay

+ pin to register delay

+ min input delay

ШчЯТМИЭМЮЊVivadoШэМўЗжЮіЕУЕНЕФhold checkЪБађБЈИцЃК

дМЪјЕФmin input delay = 8ns

data arrival time= 6.474ns

data required time= 1.045ns

ЪБађБЈИцжаslackМЦЫуЗНЪНгыЙЋЪНЭъШЋвЛжТЃЌвђДЫПЩвдЕУЕНhold slack = data arrival time ЈC data required time= 6.474ns ЈC 1.045ns = 5.429nsЁЃ