一. Demo的测试:

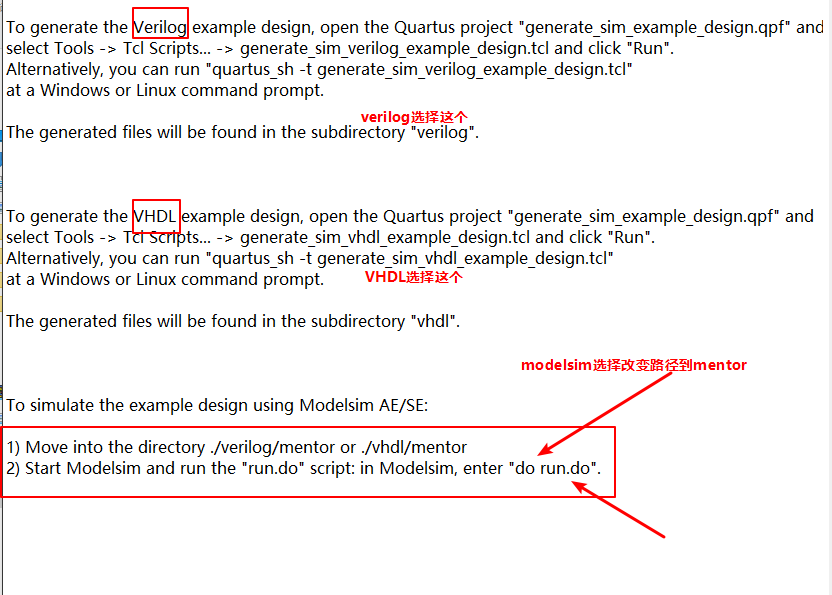

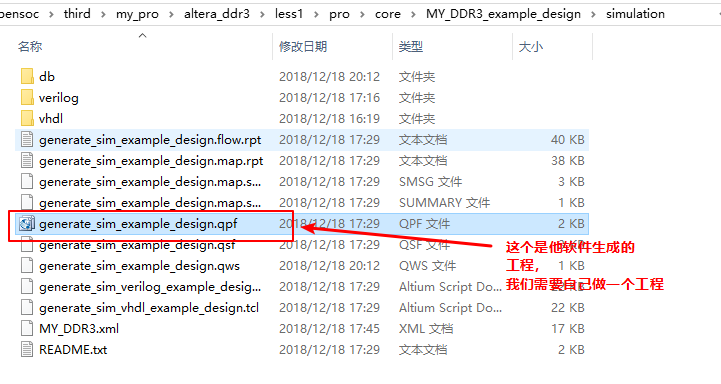

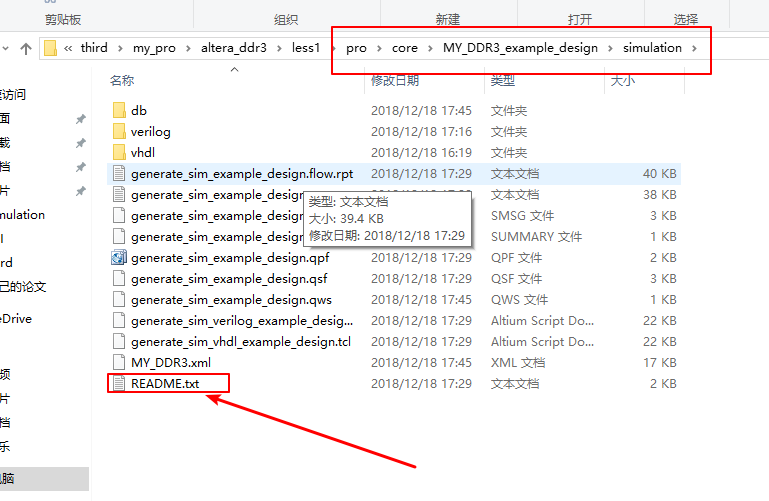

新建完一个DDR3的IP核后,在core的MY_DDR3_example_design的simulation文件夹里面有README.txt

README里面会有提示你需要有哪些步骤。

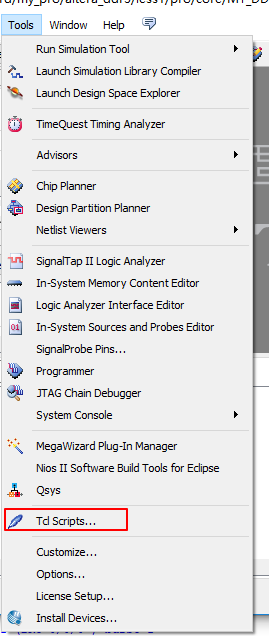

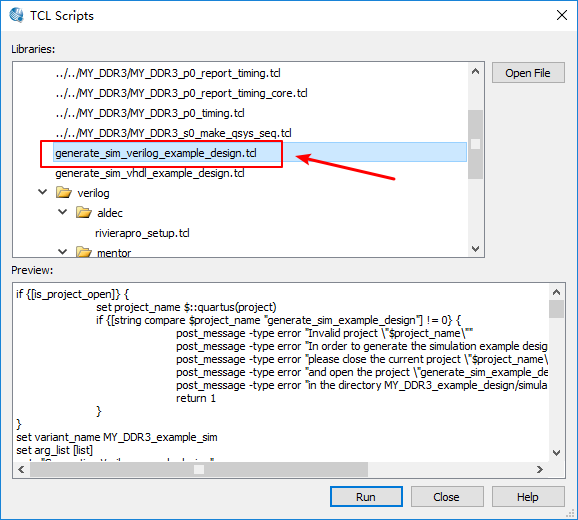

1.打开仿真的工程,然后选择运行tcl脚本tcl scripts

然后点击run一下tcl。

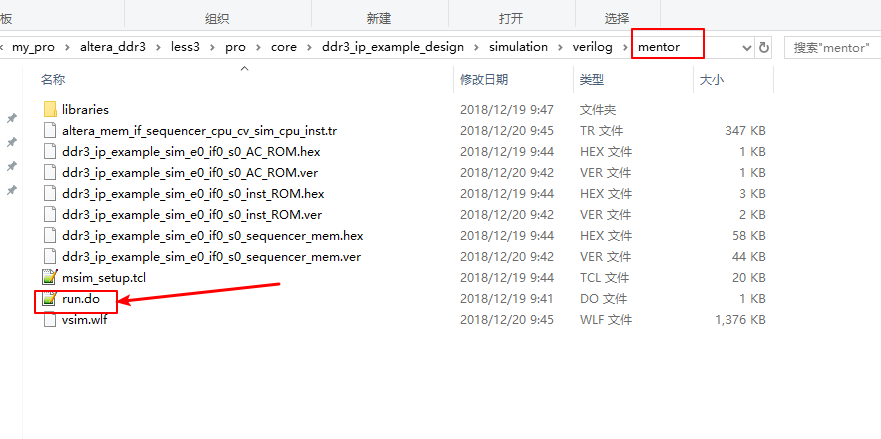

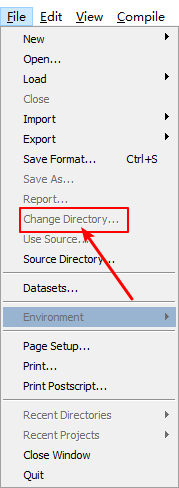

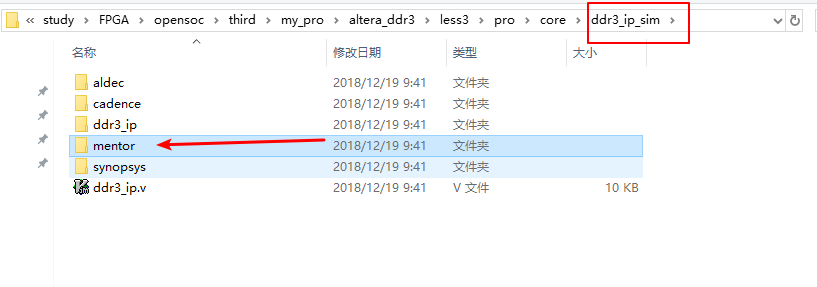

2.根据readme的提示,change Directory改变路径到verilog / ... /mentor这个路径下

然后运行路径下的do文件。

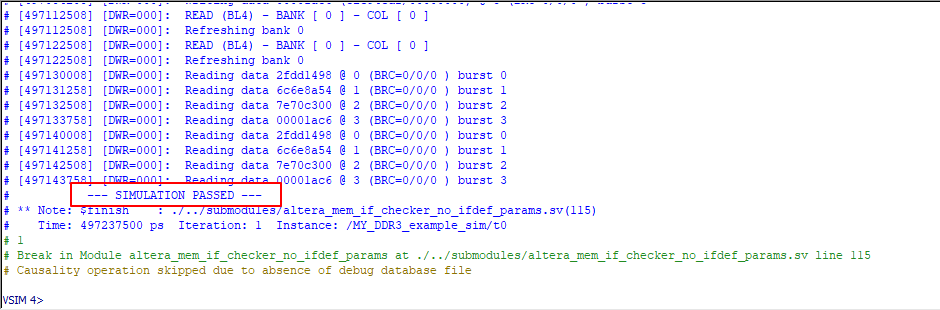

3.do完后,会提示simulation passen 仿真结束。

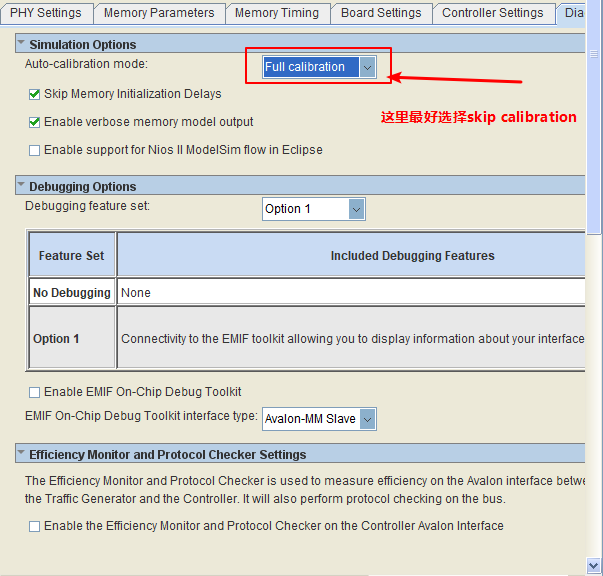

需要仿真的话,在生成IP核的时候,auto-calibration mode ――――skip calibration.

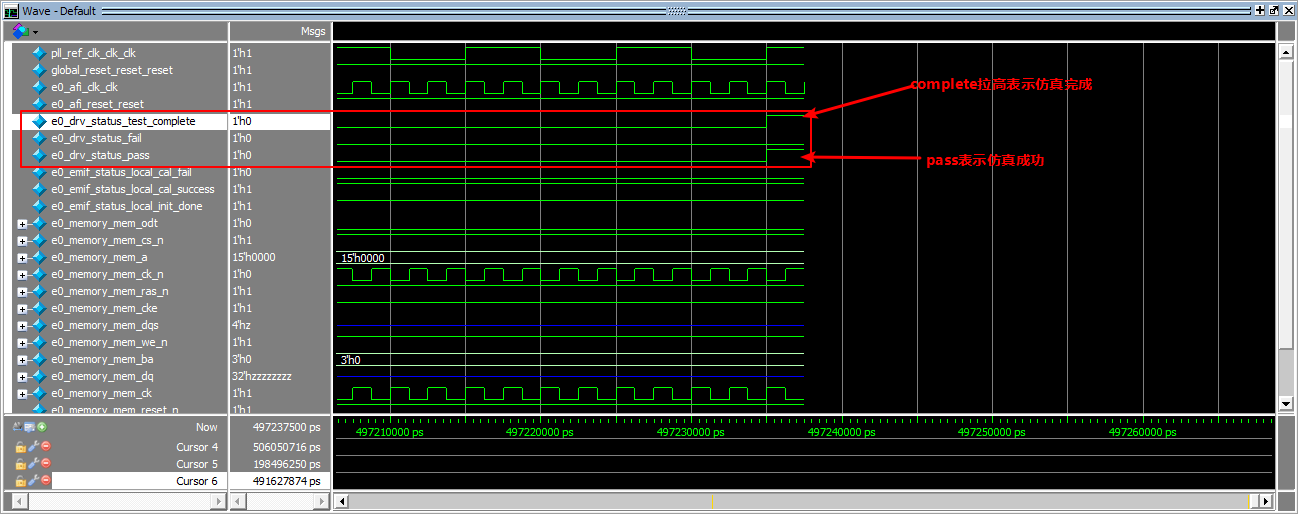

4.查看仿真波形

二:自建仿真平台:

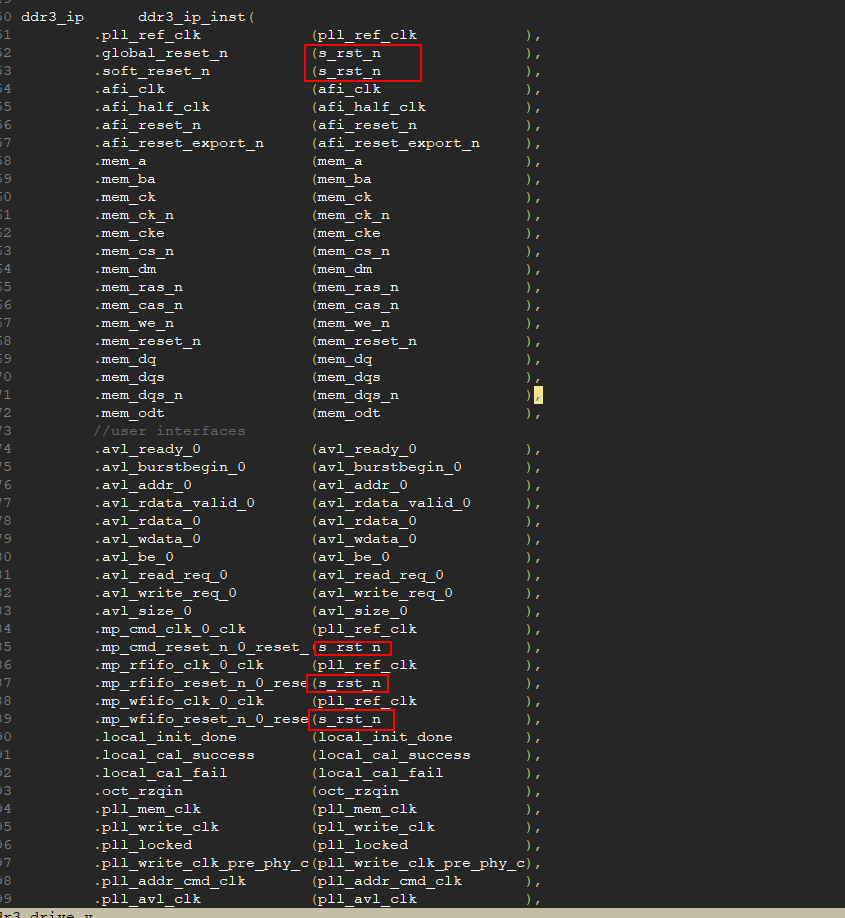

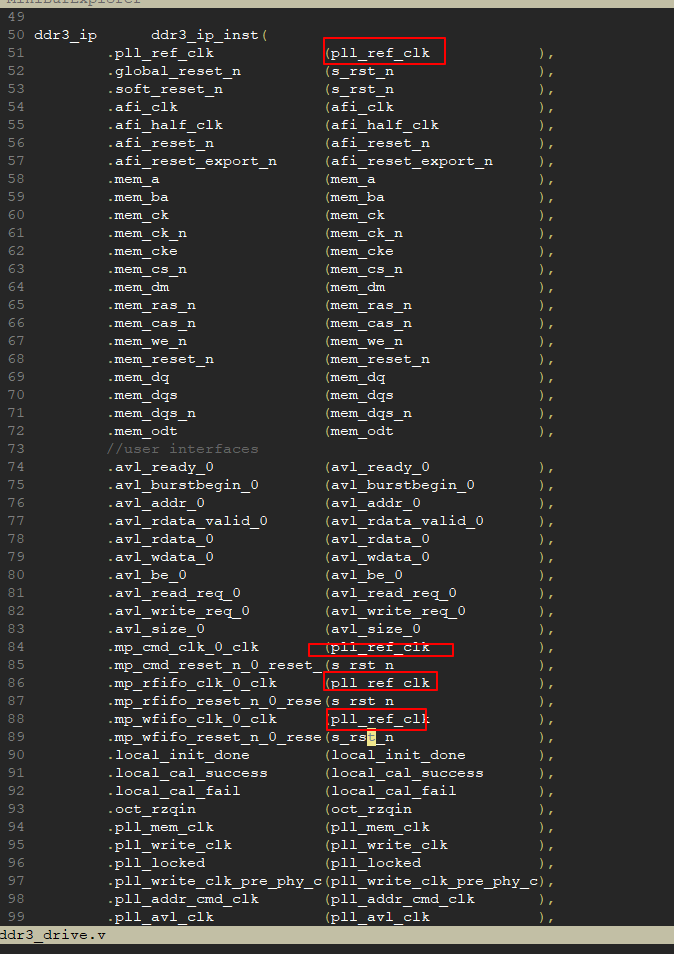

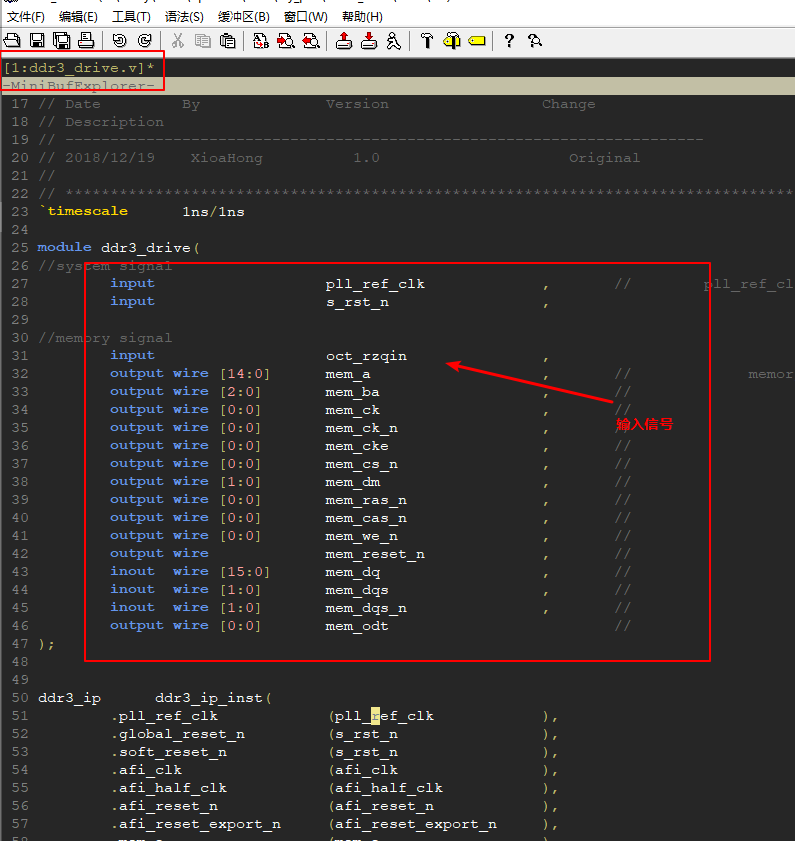

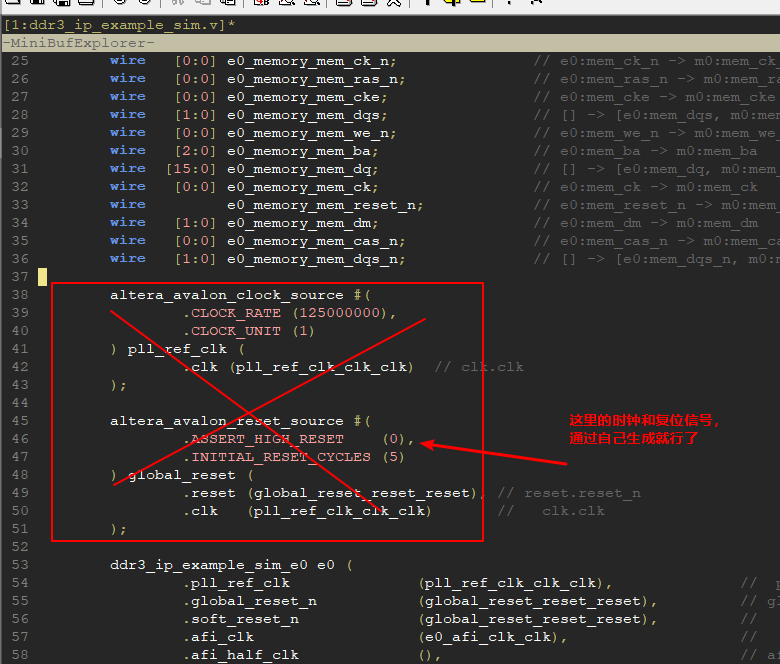

1.写例化DDR3 IP核的顶层模块,将DDR3模块IP核例化一下。并且模板中的rst改成用系统的复位信号。时钟用系统的时钟信号。

2.将sim下的mentor里面的tcl和仿真Demo中的do文件放到自己的目录下(tcl不是用这里面的tcl文件)。

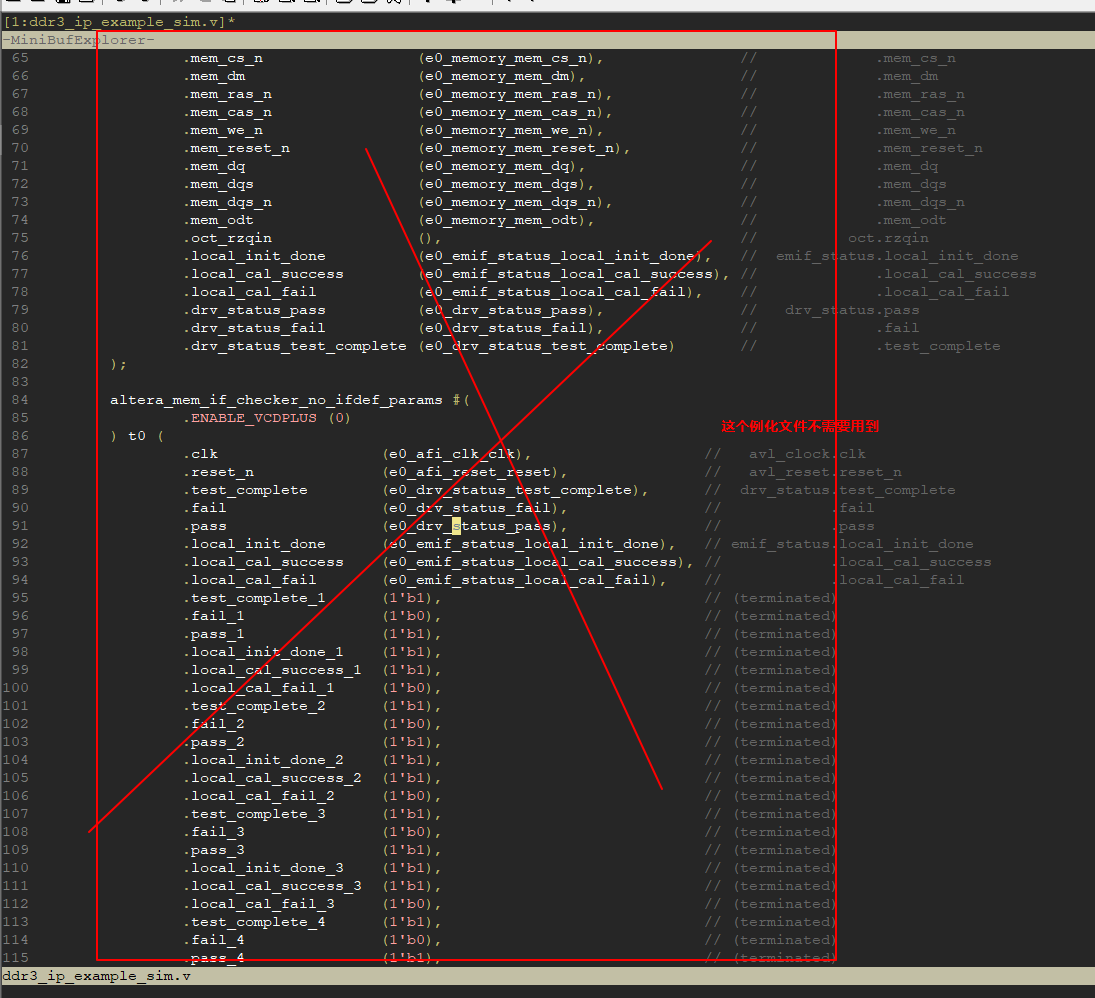

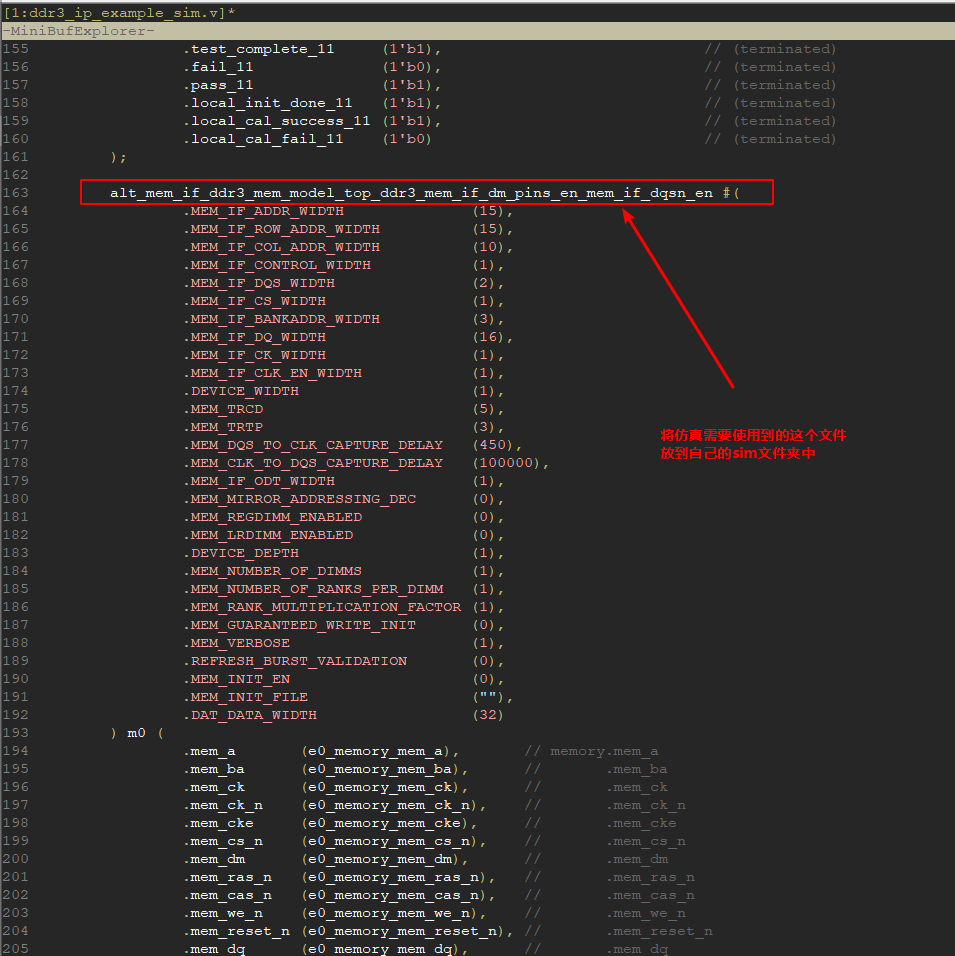

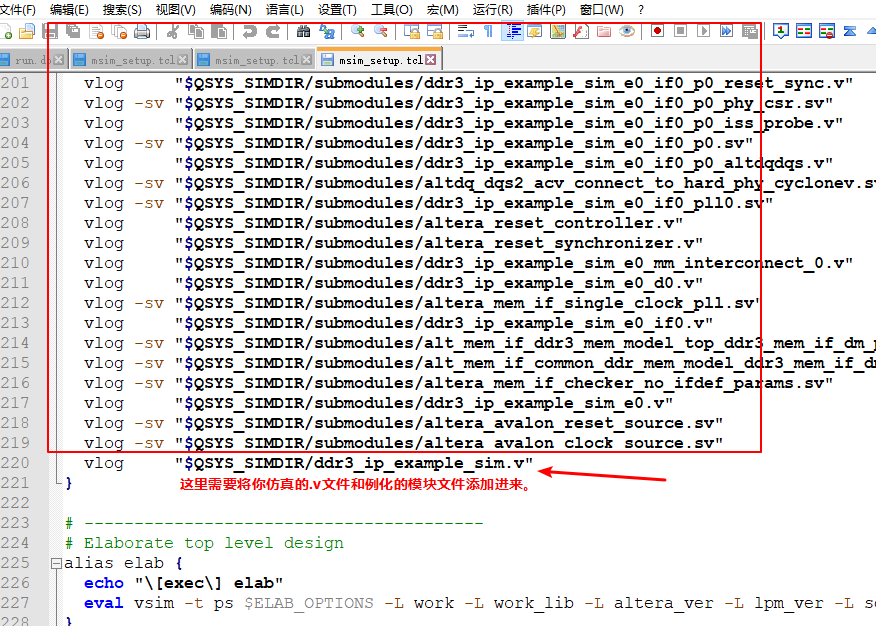

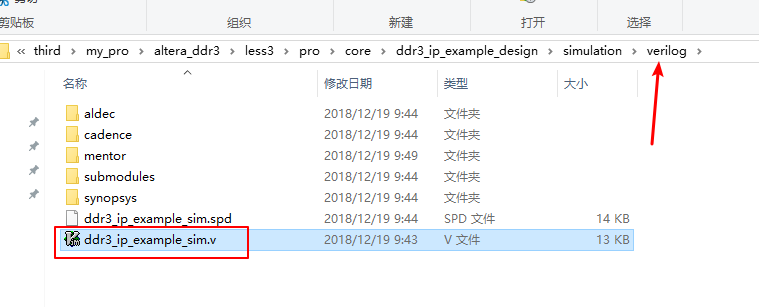

3.写仿真tb文件,模仿Demo的tb文件就行,将ddr3_ip_example_sim.v这个文件复制到自己的文件夹中,

然后将仿真文件中需要用到的文件放到sim文件夹中。

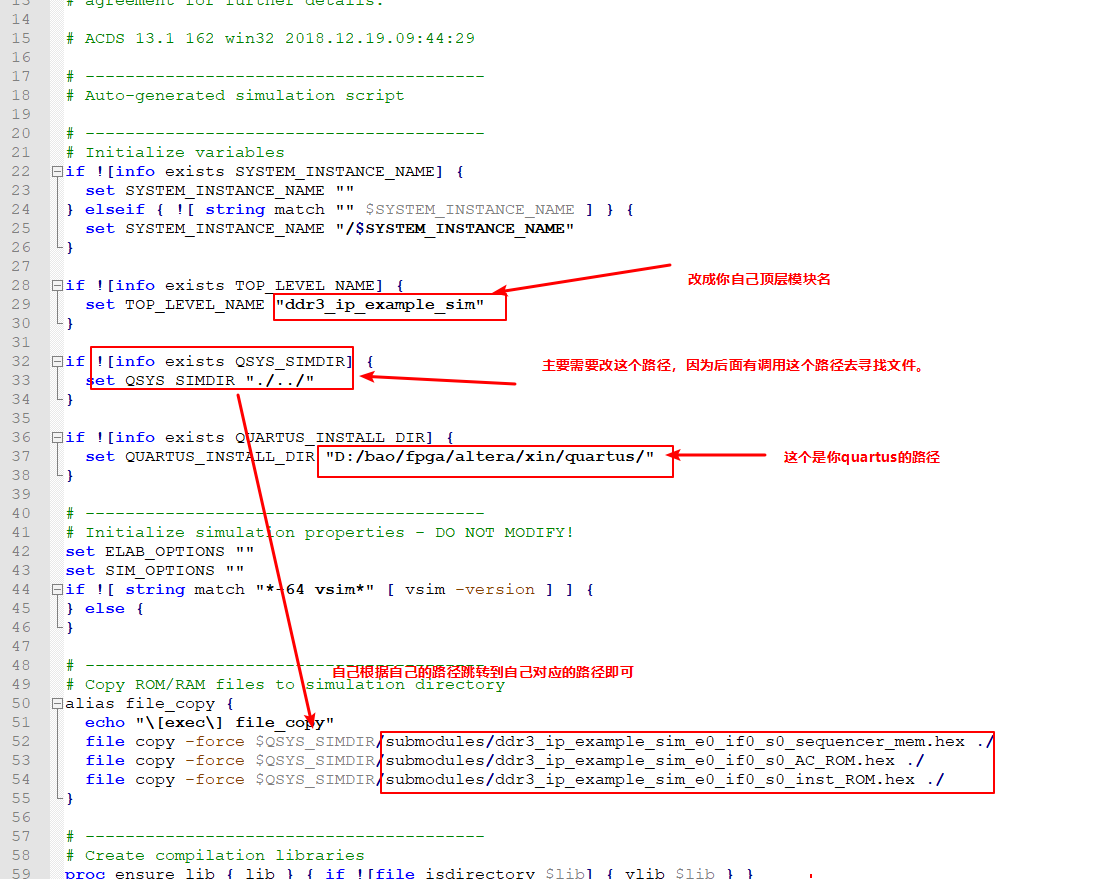

4.更改tcl脚本文件。主要是要修改TOP_LEVEL_NAME和

QSYS_SIMDIR这个路径。然后将你自己写的顶层模块添加到目录下。因为tb文件还包含了.sv后缀的文件,vlog后面要+ -sv参数去编译这个文件。

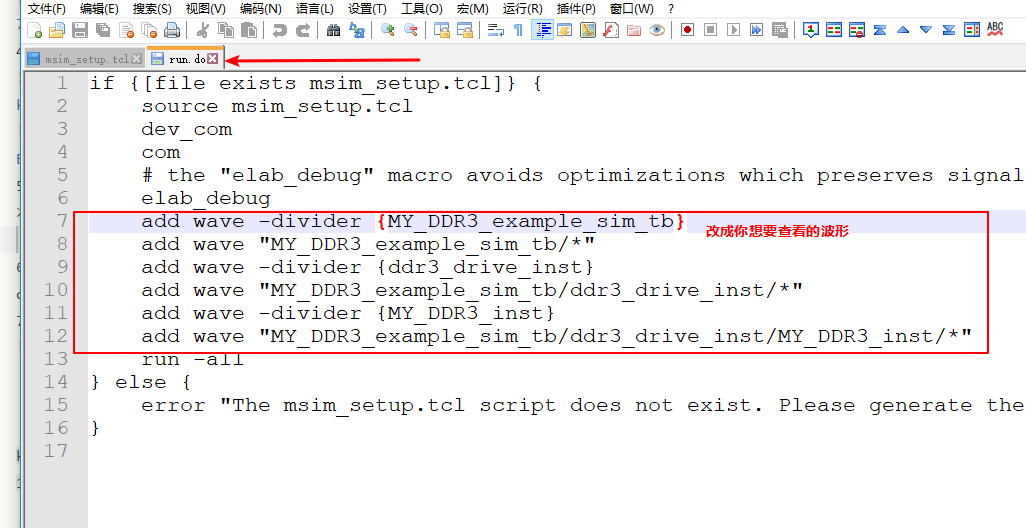

5.修改do文件

将do文件改成你自己需要观看波形的文件名,将add wave改成你想要查看波形的名字。

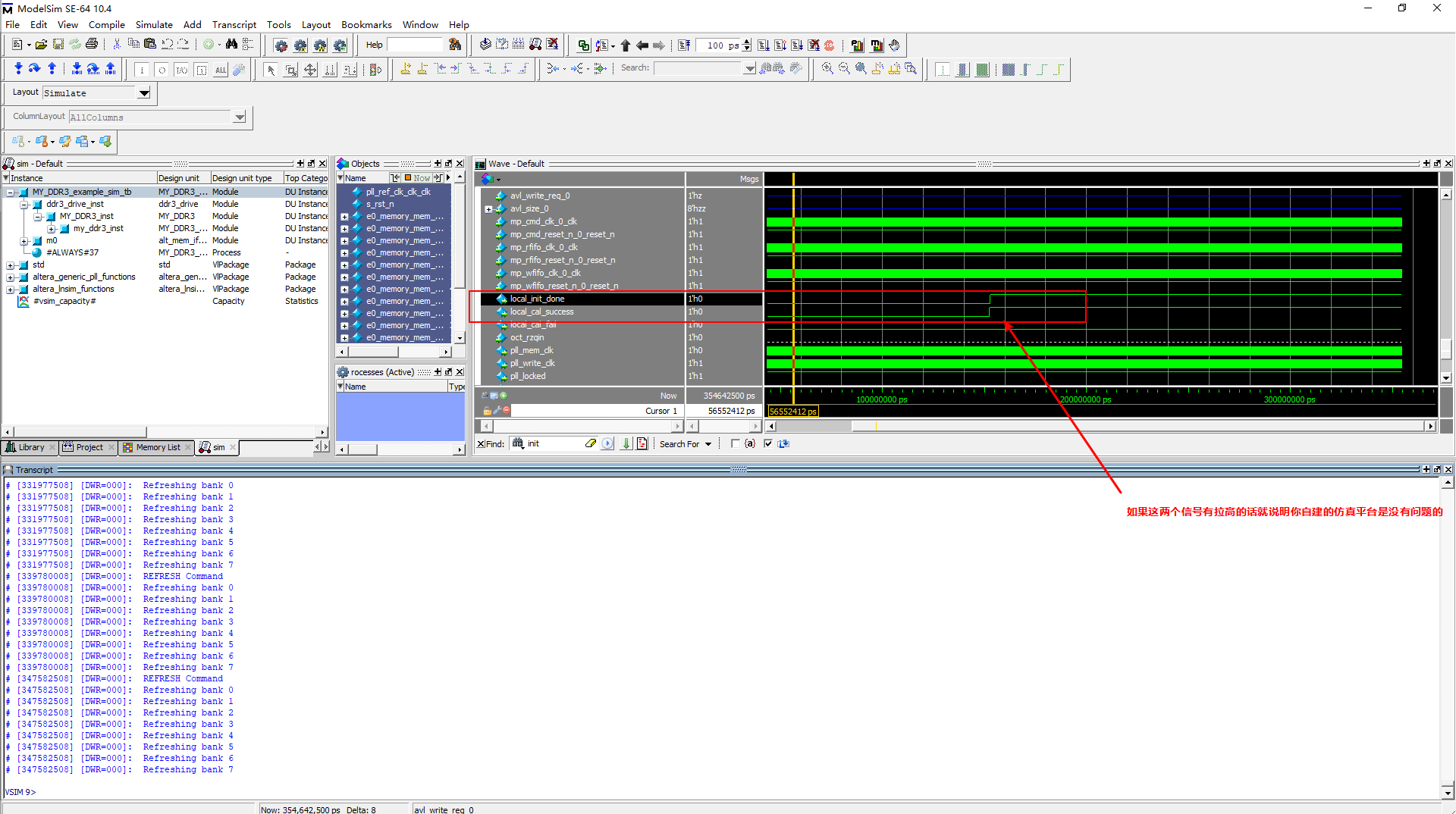

6.然后将modelsim的路径改到你自己的路径下,运行do文件即可

7.自建仿真平台的波形