Verilog学习之路(2)— Vivado 2018.3下载安装和HelloWorld

一、前言

Quartus II是Xilinx的FPGA设计工具,

二、安装包下载

百度云链接地址:https://pan.baidu.com/s/1I_bkLOsUeqELDrjdebXp1w 提取码:dn55

其他相关资料下载:http://www.corecourse.cn/forum.php?mod=viewthread&tid=28465

三、软件安装

安装包下载好后解压【Xilinx_Vivado_SDK_2018.3_1207_2324.tar.gz】,记住不要解压到中文目录,解压后找到【xsetup.exe】点击运行

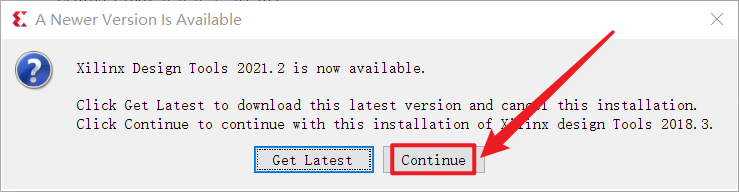

这里会跳出一个提示提醒下载最新版本,我们这里不下载,继续使用2018.3版本安装

点击【Next】下一步

将三处【I Agree】都勾选同意,然后点击下一步

选择要安装的组件,这里我们选择 【Vivado HL Design Edition】 就可以, 这就是 FPGA 开发需要的软件,然后点击【Next】。

选择要安装的一些工具组件, 这里可以保持默认。

然后选择安装目录,同样不要有中文

点击【Install】开始安装

安装过程比较慢,这里需要等一段时间。

安装过程会弹出下面的界面安装下载器驱动,点击安装。

安装完成,会弹出 Installation completed successfully,点击确认即可

安装完成会弹出 License Manager 窗口,如果没有弹出,可以在Vivado 的 Help 菜单下找到 Manage License 的窗口菜单。

将安装包目录下的【Vivado license.7z】解压到安装目录下,然后在【Manage License Search Paths】 中,将该文件路径填入LM_LICENSE_FILE 中,设置好以后点击 Set 进行保存。

点击左边窗口 View License State,可以看到右边窗口具体加载的一些 License 的情况,到此, Vivado 软件安装就完成了。

四、新建Hello工程

打开Vivado 集成开发环境,并进入到 Vivado 启动界面,如下所示,可以看到有Quick Start、 Tasks、 Learning Center 三组快速入口。

- Quick Start:包含有 Create Project(创建工程)、 Open Project(打开工程)、 Open Example Project(打开实例工程)。

- Tasks :包含有 Manage IP(管理 IP)、 Open Hardware Manager (打开硬件管理器)、Xilinx Tcl Store(Tcl 脚本存储库)。

- Learning Center :包含有 Documentation and Tutorials(文档和教程)、 Quick Take Videos(快速上手视频)、 Release Notes Guide(发布注释向导)。

我们单击 Quick Start 组的 Create Project 来新建一个 Vivado 设计工程。

接下来就会打开创建新工程的向导,出现 Create a New Vivado Project 对话框,我们单击 Next 按钮。

填入工程名称以及工程路径,我们需要注意工程路径与工程名一定不能包含空格以及中文字符,否则在后续流程中会出现错误。然后单击 Next 按钮。

这里选择 RTL 类型的工程,勾选下面的复选框 Do not specify sources at this time,不在设计创建阶段进行添加源文件。单击 Next 按钮。

选择器件,这里选择对应的芯片,这里我直接搜索xc7a35tfgg484-2,点击选择完成后单击 Next 按钮。

出现 New Project Summary 对话框,如图所示。单击 Finish 按钮,完成工程的创建。

五、新建设计

点击【 Flow Navigator】-> 【Project Manager】下的 Add Sources 选项;或者在 Sources 面板下单击“+”按钮。

我们需要的是创建 Verilog HDL 源文件,因此选中第二项 Add or Create Design Source 前面的单选按钮。单击 Next 按钮。

单击 Create File 按钮来创建一个新的源文件

选择文件的类型,输入文件的名字。单击 OK 按钮。

可以看到,出现了我们新添加的 hello.v 文件。单击界面中 Finish 按钮完成创建

出现 Define Module 对话框,我们可以在此处添加设计源文件中的顶层端口信号,如图所示。单击 OK 按钮。

双击 Sources 面板下的 led_flash.v 文件,可以在主窗口中打开 led_flash.v 文件。其中内容即为我们之前在新增源文件向导中所描述的设计端口描述,如下所示。

我们将其修改补充为如下所示,然后点击保存

module hello(input a,input b,input sel,output out);assign out = sel ? a : b;endmodule

六、RTL 描述与分析

在 Flow Navigator 下,找到 RTL Analysis,并展开。单击 Open Elaborated Design,打开 Elaborated Design。单击图中的 Schematic,打开 RTL 原理图,

如图所示。该原理图是依据 HDL 描述 生成的,根据该原理图可以查看设计是否达到要求并加以修改。