第十一课

Post-output data

Default Optimization

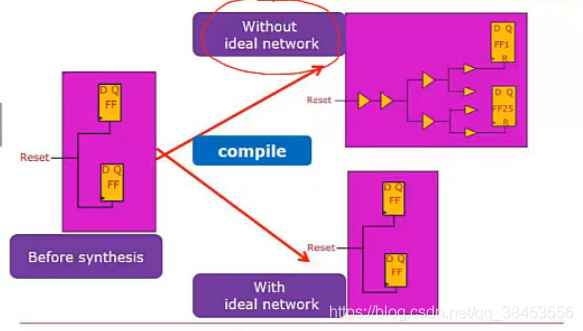

默认状态下,DC会将CLK网表和一些潜在的高扇出(HFN)网表视为理想网络,除此之外所有的电路都会考虑延迟和DRC的影响。高扇出信号包括set/reset以及select/enable。此时DC将不会对理想网络做额外的优化,高扇出网表的优化将在后端中完成。

set_ideal_network [get_ports reset]

set_ideal_netword [get_pins CTRL_reg/Q]

set_ideal_network -no_propagate [get_nets CTRL]

#设置理想网络时,实质上是对网络的所有端口设置理想状态

**注:只有当逻辑门的所有输入端是理想网络,输出端才会变为理想网络。

可以用一些命令为理想网络初步建立模型:

set_ideal_network [get_ports rst]

set_ideal_latency 1.8 [get_ports rst]

set_ideal trasition 0.5 [get_ports rst]

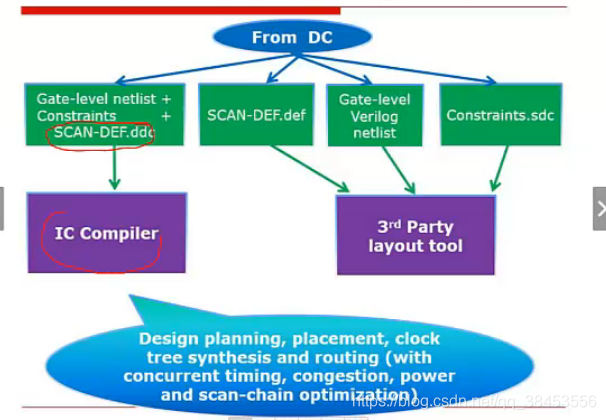

- What is sdc?

第三方的版图工具无法理解DC的约束,利用.sdc文件可以将约束转换为通用的格式。

Netlist restrictions

- assign语句

assign语句实际上是行为级的描述,因此在以下情况中尽量不要使用assign语句而是使用模块例化:多端口网络以及三态门。

verilog中尽量只保留四种类型:wire,register,integer,genvar.

有时从语法上电路没有问题,但是综合时会出现问题。

可以使用以下命令避免多端口网络(multiple port nets)和三态门:

set_fix_multiple_port_nets -all -buffer_constraints

#-all表明对所有多端口网络适用,-buffer_constraints表明用插入buffer的方式优化。

set_app_var verilogout_no_tri true

#这个命令可以自动将tri转化为wire

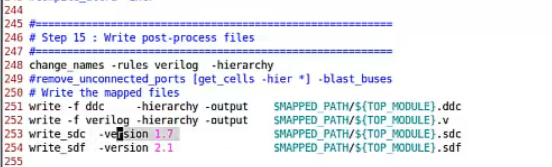

- change_name

在dc生成网表的过程中可能会出现出现网络名称后端无法识别的情况,这时要用change_name命令:

set_app_var verilogout no_tri true

change_names -rules_verilog -hier

#在生成verilog文件之前改变命名规则

write -f verilog -out <netlist_name>

实例

set_isolate_ports -type buffer [get_ports q_o]

可以在外部电路和内部电路间插入缓冲单元

set_app_var verilogout_show_unconnected_pins true

可以显示没有连接的端口