文章目录

-

- PAE模式 2-9-9-12分页

-

- 非PAE模式为什么是10-10-12

- PAE模式为什么是2-9-9-12

-

- 总结

- PDPTE结构

- PTE结构

- PTE结构

- XD标志位(AMD中称为NX,即No Excetion)

PAE模式 2-9-9-12分页

非PAE模式为什么是10-10-12

- 先确定了页的大小4K,所以后面12位的功能也就确定了。2的12次方为4096,也就是4KB。12位正好可以索引到每一个物理地址。

- 当初的物理内存比较小,所以4个字节的PTE就够了,加上页的尺寸是4K。所以一个页能存储1024个PTE,也就是2的10次方,第二个10也就确定了。2的10次方为1024,所以PTI确定为10

- 剩下的10位PDI,10+10+12刚好32位

PAE模式为什么是2-9-9-12

在非PAE模式下,由于物理地址长度为32位。所以内存范围在0-0xFFFFFFFF之间,也就是2的32次方,也就是4GB。

CPU的寻址范围取决于物理地址的长度。CPU要想寻址到4GB以外的内存空间。就必须增大物理地址的长度。

例如下面的地址:

10-10-12:0x12345678

PDE:FFFFF123(32)

PTE:FFFFF123(32)

物理地址:FFFFF678(32)

物理页起始地址:FFFFF000(32)

32位的物理地址可以寻址到4GB,那么如果增大物理地址长度到36位,就可以寻址到64GB。事实上非PAE模式下的2-9-9-12的物理地址长度就是36位。

CPU->0-FFFFFFFFF(36)

2-9-9-12(36)

那么问题来了,当物理地址扩大到36位的时候,32位的PTE自然也要发生变化。例如下面的这个地址

FFBFF123(32)

后面12位0x123肯定是不能动的,这三位是属性。前面20位是物理地址。那么就只有把前面20位拉长来突破4GB。将地址变成下面的36位地址

FFBFFF123(36)

这样的话,PTE就由原先的32位拉长到36位,能寻址到64GB的空间。

但是一旦拉长,就不是4字节对齐了;没有做到字节对齐就会影响程序的执行效率。CPU的做法是牺牲空间换时间,将原来的4字节的PTE变成8字节。

原先能保存1024个PTE成员的PTT表,现在只能保存512个PTE了。想要索引到512个成员需要9个二进制位。2的9次方等于512。这个就是2-9-9-12分页的第三个9的来源

以此类推,PDE也由4个字节变成了8个字节。数据项也由1024变成了512。PDE需要增大到8字节的原因在于如果还是保持原来的4字节,就无法索引到4GB以外的PTE了。所以PDE需要跟随PTE增大了8个字节

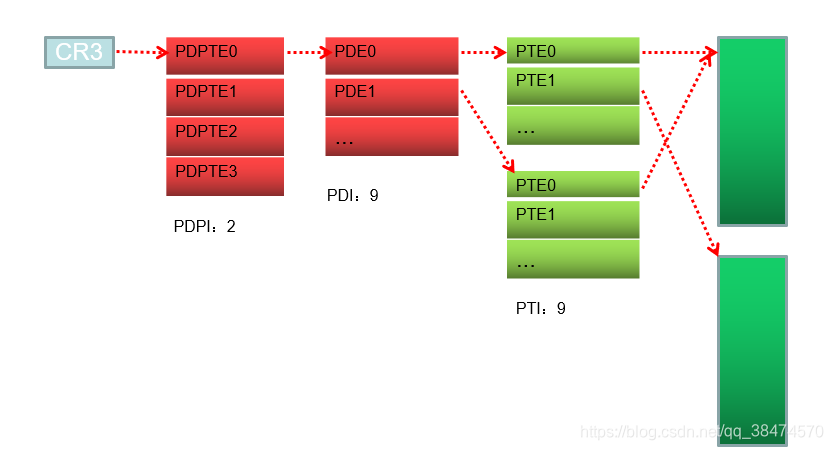

2的来源:在PDT和PTT的基础上多了一张页目录指针表PDPTE(Page-Directory-Point-Table-Entry),每项占8个字节。表里面一共4个成员。(因为一共只有两位,2的2次方等于4)如图:

总结

2-9-9-12的来源

- 12:物理页的大小为4KB,4096字节。想要索引到每一个字节需要12个二进制位。因为2的12次方等于4096。所以是12

- 9:由于PTE增加到36位,原先能保存1024个PTE成员的PTT表,现在只能保存512个PTE了。想要索引到512个成员需要9个二进制位。2的9次方等于512。

- 9:PDE跟随PTE由原来的4个字节变成了8个字节。数据项也由1024变成了512。

- 2:PDPTE的成员有4个,正好用两个二进制位索引。

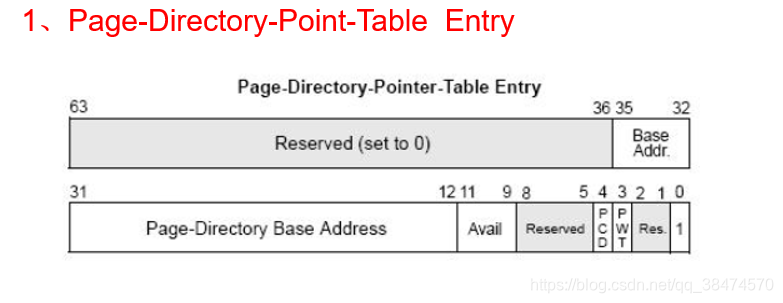

PDPTE结构

- PDPTE共有4项

- 灰色部分为保留项

- 35-12存储的是页目录表的基址,低12位补0,共36位,即页目录基址

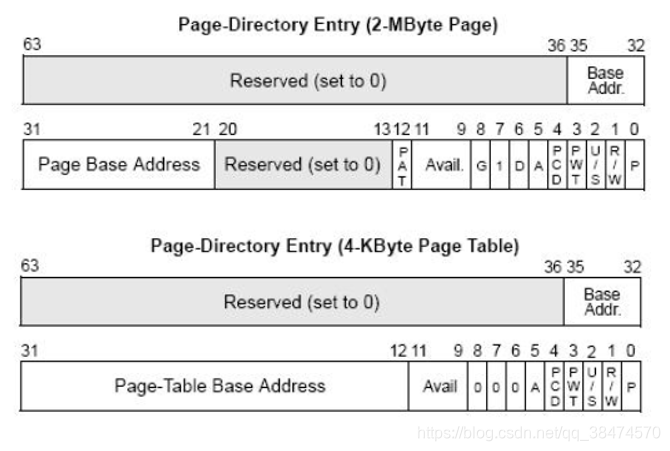

PTE结构

- 当PS=1时是大页,35-21位是大页的物理地址,这样36位的物理地址的低21位为0,这就意味着页的大小为,且都是对齐

- 当PS=0时,35-12位是页表基址,低12位补0,共36位

PTE结构

- PTE中35-12是物理页基址,24位,低12位补0

- 物理页基址+12位的页内偏移指向具体数据

XD标志位(AMD中称为NX,即No Excetion)

段的属性有可读可写可执行,页的属性有可读 可写。为了填补上没有可执行位的这个坑,Initel就做了硬件保护,做了一个不可执行位。XD=1时,表示不可执行。在PAE分页模式下,PDE与PTE的最高位为XD/NX位。

读 可写。为了填补上没有可执行位的这个坑,Initel就做了硬件保护,做了一个不可执行位。XD=1时,表示不可执行。在PAE分页模式下,PDE与PTE的最高位为XD/NX位。