这一部分描述了嵌套向量中断控制器和它使用到的寄存器。NVIC支持:

高达81个中断(根据STM32设备的型号,参照数据手册);

对每个中断可编程优先级级别0-15,一个高的优先级级别相应着较低的优先级,所以级别0是最高的中断优先级;

中断信号的电平和脉冲检测;

动态调整中断优先级;

将优先级值分组为组优先级和子优先级域;

中断平衡链;

一个外部不可屏蔽中断;

处理器在异常进入时自动将其状态堆栈,并在异常退出时卸载此状态,而不需要指令开销,这支持晚到异常处理。

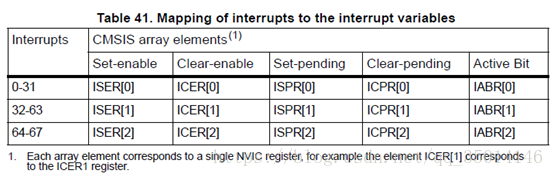

Cortex-M3NVIC寄存器CMSIS地图。为了改善软件效率,CMSIS简化了NVIC寄存器展示。在CMSIS中:

设置使能、清除使能、设置待定、清除待定、和激活位寄存器映射到32位整型数组。所以,数组ISER[0]~ISER[1]相应于寄存器ISER0~ISER2;数组ICER[0]~ICER[1]相应于寄存器ICER0~ICER2;数组ISPR[0]~ISPR[1]相应于寄存器ISPR0~ISPR2;数组ICPR[0]~ICPR[1]相应于寄存器ICPR0~ICPR2;数组IABR[0]~IABR[1]相应于寄存器IABR0~IABR2;

中断优先级寄存器的8位域映射到一个8位整型数组,所以数组IP[0]到IP[2]相应于寄存器IPR0-IPR67,而且数组入口IP[n]为中断n保存着中断优先级。

CISIS提供了线程安全代码,给出了原子访问中断优先级寄存器。

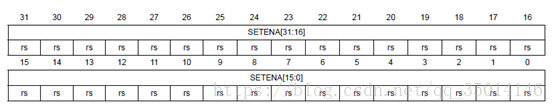

中断设置使能寄存器(NVIC_ISERx)

地址偏移 0x00~0x0B

复位值 0x0000 0000

需要的特权 特权的

位31:0 STENA[31:0] 中断设置使能位

写:

0, 无效果

1, 使能中断

读:

0, 中断失能

1, 中断使能

对应于寄存器的每位的中断。如果一个推迟中断被使能,NVIC根据它的优先级激活这个中断。如果一个中断没有被使能,断言声明它的中断信号改变中断状态为待解决,但是NVIC不会激活这个中断而不管它的优先级。

中断清除使能寄存器(NVIC_ICERx)

地址偏移 0x00~0x0B

复位值 0x0000 0000

需要的特权 特权的

ICER0-ICER2寄存器失能中断,并且显示哪些中断使能。

位31:0 CLRENA[31:0] 中断清除使能位

写:

0, 无效果

1, 失能中断

读:

0, 中断失能

1, 中断使能

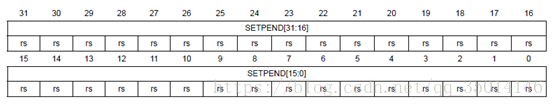

中断设置待定寄存器(NVIC_ISPRx)

地址偏移 0x00~0x0B

复位值 0x0000 0000

需要的特权 特权的

ISPR0-ISPR2寄存器强制使中断进入待定状态,并且显示哪些中断处于待定状态。

位31:0 SETPEND[31:0]中断设置待定位

写:

0, 无效果

1, 改变中断的状态为待定状态

读:

0, 中断不是待定状态

1, 中断是待定状态

写1到ISPR位,若对应的中断处于待定状态,无效果;

写1到ISPR位,若对应的是一个失能中断,设置中断的状态为待定状态。

中断清除待定寄存器(NVIC_ICPRx)

地址偏移 0x00~0x0B

复位值 0x0000 0000

需要的特权 特权的

ICPR0-ICPR2寄存器移除中断中的待定状态,并且显示哪些中断处于待定状态。

位31:0 CLRPEND[31:0]中断清除待定位

写:

0 无效果

1 移除一个中断离开待定状态

读:

0中断不是待定状态

1中断是待定状态

写1到ICPR位,不影响相应中断的激活状态。

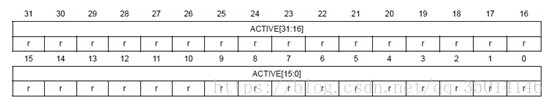

中断活跃位寄存器(NVIC_IABRx)

地址偏移 0x00~0x0B

复位值 0x0000 0000

需要的特权 特权的

IABR0-IABR2寄存器显示哪些中断处于活跃状态。

位31:0 ACTIVE[31:0]中断活跃标志

0中断不是活跃状态

1中断是活跃状态

如果对应中断处于活跃状态或活跃和等待状态,这个位读为1

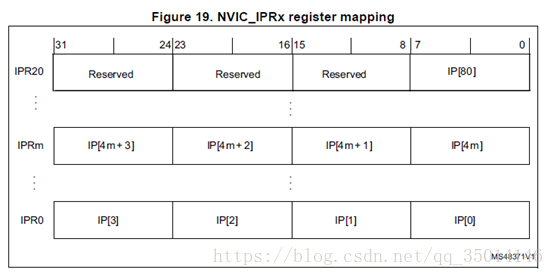

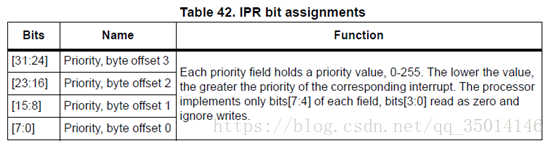

中断优先级寄存器(NVIC_IPRx)

地址偏移 0x00~0x0B

复位值 0x0000 0000

需要的特权 特权的

IPR0-IPR16寄存器为每一中断提供了4位优先级域,那些寄存器都是字节可访问的。每一个寄存器保存4个优先级域,CMSIS中断优先级数组IP[0]到IP[67]如下展示。

每一个优先级域都保存一个优先级值0-255。值越小,相应中断的优先级越大。处理器只执行每个区域位[7:4],位[3:0]读为0且忽略写。

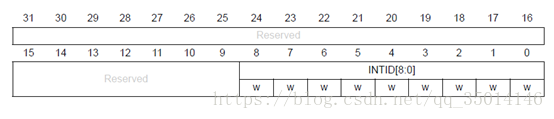

软件触发中断寄存器(NVIC_STIRx)

地址偏移 0xE00

复位值 0x0000 0000

需要的特权 当在SCR中的USERSETMPEND位为1时,无特权的软件可以访问STIR。只有特权的软件可以使能非特权访问STIR。

位31:9 保留,必须保持清除的

位8:0 NTID[8:0] 软件生成中断ID。写入STIR会生成一个软件生成的中断(SGI),被写入的这个值是所需要的SGI的中断ID,在范围0-239。例如,一个0b0000 00011指定中断IRQ3。

电平敏感和脉冲中断。STM32中断是电平敏感和脉冲敏感的,脉冲敏感也被描述为边沿触发中断。

一个电平敏感的中断保持声称的直到外设解除声称的中断信号,典型地,这发生因为ISR访问外设,导致外设清除中断请求。一个脉冲中断是一个由处理器时钟上升沿同步采样的中断信号,为了确保NVIC检测到中断,在NVIC检测到脉冲并且锁存中断,外设必须声称中断信号至少一个时钟周期。

中断的硬件和软件控制,Cortex-M3锁存所有中断。一个外设中断变成待定状态因为以下原因之一:NVIC检测中断信号是高并且终端没有处于活跃状态;NVIC检测到中断信号的上升沿;软件写入相应中断的设置待定寄存器位,或写入STIR产生一个待定的SGI。

一个待定中断保持中断直到一个以下条件出现:

处理器进入中断的ISR,这将改变中断的状态从待定到活跃,对于一个电平敏感中断,当处理器从ISR返回,NVIC采样中断信号,如果信号被声称,中断的状态变化为待定,这可能导致处理器快速的重新进入ISR,否则,中断的状态变化为不活跃状态。对于一个脉冲中断,NVIC继续监测中断信号,如果存在脉冲,中断的状态从待定变化为待定和活跃状态。在这种情况下,当处理器从ISR返回时,中断的状态变化为待定状态,这可能导致处理快速重新进入ISR。当处理器在ISR中时,如果中断信号不是脉冲的,处理器从ISR返回时,中断的状态变化为不活跃状态。

软件写相应中断的中断清除待定寄存器位。对于一个电平敏感的中断,如果中断信号仍旧是声称的,中断的状态不发生变化。否则,中断的状态变化为不活跃状态。对于脉冲中断,中断的状态变化为:如果状态是待定状态,变为不活跃状态;如果状态是活跃和待定状态,活跃状态。

NVIC设计提示和小技巧。确保软件使用正确地对齐寄存器访问,处理器不支持不对齐的NVIC寄存器访问。查看单独的寄存器描述所支持的访问大小。一个中断可以进入待定状态即使它未被使能。在编写VTOR重新安置向量表时,确保新向量表的向量表入口设置为错误处理,NMI和所有其它类似中断可以使能的异常。

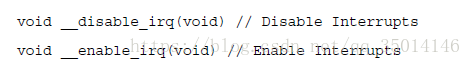

软件可以使用CPSIE I 和CPSID I 指令使能和失能中断。CMSIS提供了以下指令函数用于那些指令。

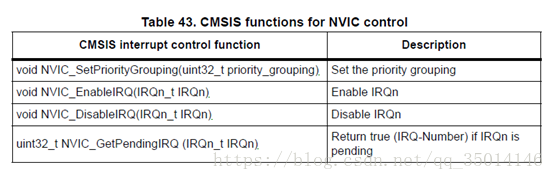

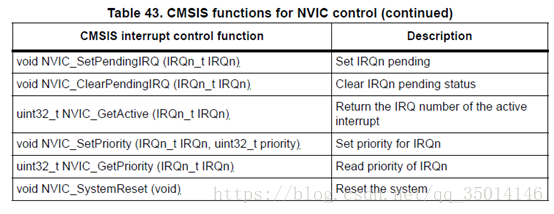

此外,CMSIS提供了许多NVIC控制的函数,包括:

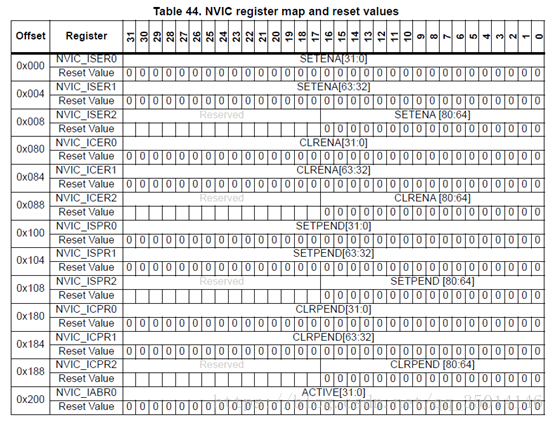

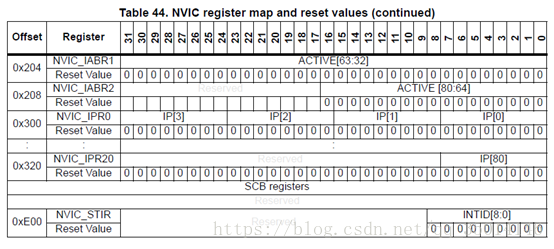

下表提供显示了NVIC寄存器地图和复位值。NVIC主寄存器块的基地址为0xE000 E100。NVIC_STIR寄存器位于0xE000 EF00独立的块。