抢答器

一、 实验目的

- 综合运用 D 触发器、门控时钟、计数器等。

- 用 LED 和数码管显示抢答成功的组号。

- 了解小型综合数字系统实验的调试和故障排除方法。

二、 实验原理及内容

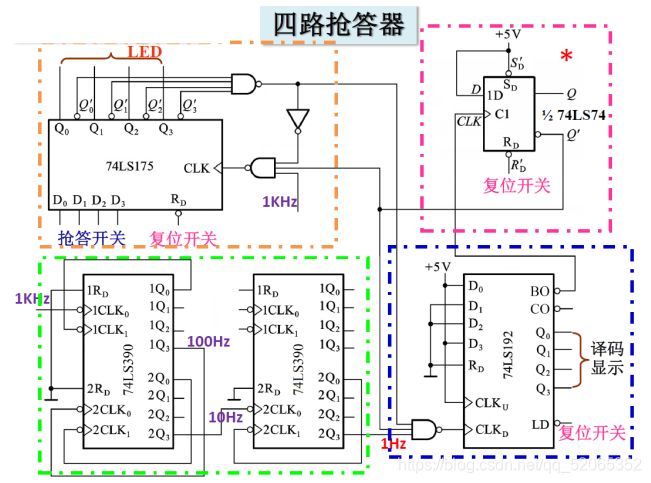

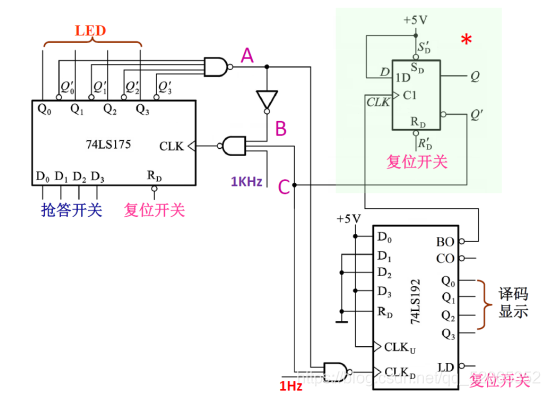

完整的实验电路图如下图:

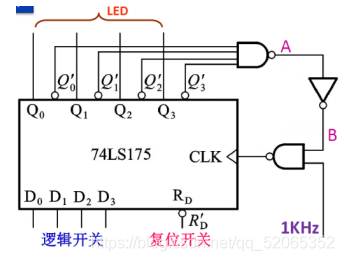

1.抢答模块

抢答模块电路如下:

抢答开始前,由主持人按下??复位开关, 74LS175 的?0-?3的输出为 0。当抢答开

始后,反应最快的参赛者按下开关,对应的 LED 点亮,同时,切断了 74LS175 的时钟信

号,电路不再接受其他参赛者的抢答。

2.数码管显示模块

将抢答模块输出换接为数码管,并用或门设计相应电路图,使数码管显示抢答成功

的组号。

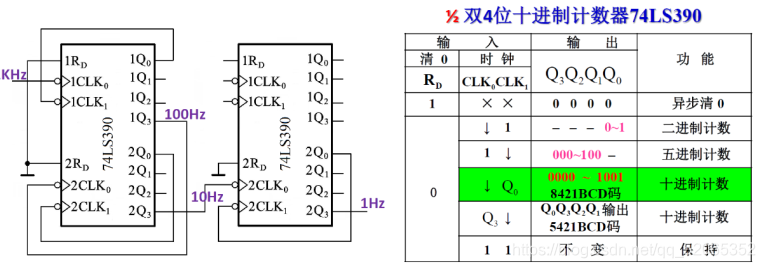

3.分频模块

分频模块电路及双 4 位十进制计数器 74LS390 功能表如下:

由功能表分析电路可知,每一个 7 输出信号频率为输入信号频率的十分之一,则输

入 1KHz 信号经过三次分频就可以得到 1Hz 的输出信号。

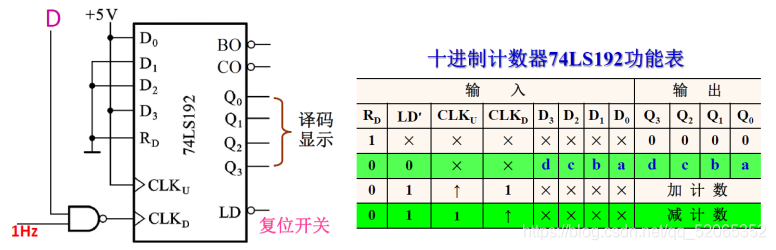

4. 倒计时模块

倒计时模块电路及十进制计数器 74LS192 功能表如下:

由功能表分析电路可知,使用减计数,从预设数 9 开始,由于输入时钟信号频率为

1Hz,故每秒倒计时一次,输入 D=0 时不倒计时。

5. D 触发器

D 触发器位于完整电路图右上角。本次采用的是边沿触发的 D 触发器。当倒计时模

块从 0 又到 9 时,输出端 BO 会产生一个负脉冲,此时 D 触发器输出端 Q=1,?′ = 0,

从而使倒计时模块停止倒计时,可实现锁“9”的功能。

三、 实验结果

1.测试各逻辑门和触发器的逻辑功能

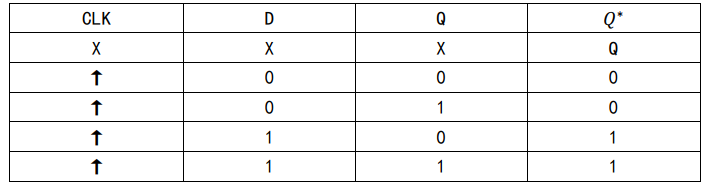

测试 D 触发器的逻辑功能,得到如下特性表:

D 触发器特性方程为?? = ?.

2.测试抢答模块电路功能

测试得知,初始时输出全为 0.将??置为高电平,当??最先置为 1 时,对应??输出

为 1,其余为 0,并且即使其他输入端此时输入高电平,对应的输出端也不会输出高电

平。将输入端恢复为 0,复位开关??置为低电平又置为高电平后,又可重复上述过程,

则抢答模块功能正常。

3.试实现在一个数码管上显示抢答成功的组号,画出电路图。

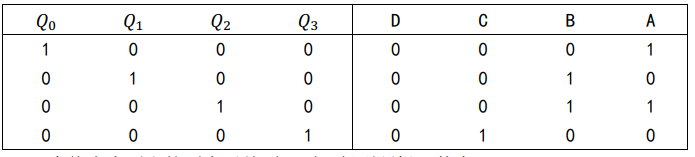

先列出 74LS175 输出端与数码管输入端对应的真值表:

真值表未列出的项为无关项,则可得到逻辑函数为:

? = ?0 + ?2 , ? = ?1 + ?2 ,? = ?3 , ? = 0

根据真值表画出电路图为:

连接好电路后,再次模拟抢答操作,数码管显示符合实验要求。

4.搭建分频模块,用示波器测量其输出频率

使用示波器调节输入端信号频率,使其等于 1KHz,再测量第一片 74LS390 输出信

号频率。实验测得输入频率为 1.037KHz,输出频率为 10.37KHz,由于第一片 74LS390

经过了两次分频,输出变为百分之一,故分频模块功能无误。

5.测试计数器 74LS192 功能后接入电路中

将 74LS192 输出端?0到?3依次接到数码管的 A、 B、 C、 D 端。给 CL??端通入 1Hz 的

脉冲信号。先给 LD 通入高电平, 由于预设数为 9,当 LD 置为低电平时,数码管显示从

9 每秒一次开始倒计时,到 0 后又再次从 9 开始。

6.倒计时模块中增加 D 触发器,实现锁 9 功能,直到按下复位开关。

将各模块连接在一起得到总电路图如下,其中 1Hz 脉冲由分频模块提供。

(1) 计时器显示答题时间

当计时器的 D 端接抢答模块 A 端时,计时器显示为答题时间。主持人将复

位开关从低电平拨至高电平,此时可以开始抢答。抢答前, A 端输出为 0,计

时模块不计时,显示为 0。当某一组抢答成功后,抢答模块显示其组号,其他

组不能进行抢答,此时 A 端输出为 1,计时模块开始计时, 从 9 每秒一次倒数

计时直到重新返回 9.此时 BO 产生一个负脉冲, D 触发器将?′置为 0 从 C 端,

使计数器????恒为高电平,计数器停止计数,锁定为“9” .主持人拨下复位开

关,并且将抢答端开关复位后,可以开始新一轮的抢答。

(2) 计时器显示抢答时间

当计时器的 D 端接抢答模块 B 端时,计时器显示为抢答时间。 初始时复位

开关为高电平。 主持人将复位开关从低电平拨至高电平,开始抢答。 此时, B

端输出为 1,计时器开始计时。 当某一组在计时器返回到 9 之前抢答成功时,

抢答模块显示其组号,其他组不能进行抢答,此时 B 端输出为 0,计时模块停

止计时;若没有任意组抢答成功,则此时 BO 产生一个负脉冲, D 触发器将?′

置为 0 从 C 端,使计数器????恒为高电平,计数器停止计数,锁定为“9” .

主持人拨下复位开关,并且将抢答端开关复位后,可以开始新一轮的抢答。

四、思考题

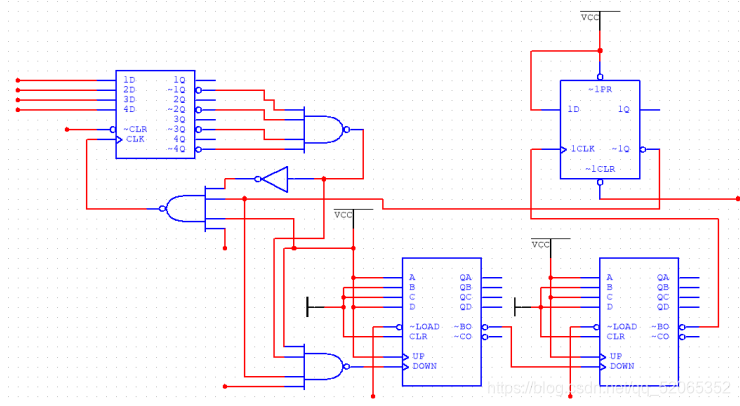

问题: 在本实验的基础上设计一个 60 秒的答题倒计时电路, 要求计时显示精确到秒。

解答:

设计思路: 60 秒的计数器需要给两个数码管提供输入。 一个从 5 开始且每隔 10 秒

倒数一次作为 10 位, 一个从 9 开始且每隔 1 秒倒数一次作为个位。 一种自然的想法是

再使用一片 74LS192, 利用前一片从 0 到 9 时 BO 端输出的一个负脉冲来为下一片计时,

并且此时两片 74LS192 的锁 5 与锁 9 功能由第二片的 BO 端连接 D 触发器来实现。

设计电路:

上述电路中 74LS175 输出端用实验 3 的电路接入数码管, 两片 74LS192 输出端分

别从高位到低位接入两个数码管。

五、 反思总结

本次实验属于综合性实验, 若要完成整个实验, 每一个模块都不能有误, 因此在将每个

模块连接在一起之前需要单独检查每个模块是否正常工作。 由于接线非常多, 若有一根导线

出现问题则很可能检查不出错误的来源, 所以接线之前先检查导线连接是否良好也是非常必

要的。