1、参考 https://www.cnblogs.com/wpqwpq/p/6954296.html

2、参考https://blog.csdn.net/linbian1168/article/details/105011187?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522162121891316780255220576%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fall.%2522%257D&request_id=162121891316780255220576&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~all~first_rank_v2~rank_v29-10-105011187.pc_search_result_no_baidu_js&utm_term=xilinx++7%E7%B3%BB%E5%88%97+CAM&spm=1018.2226.3001.4187

1、xapp1151_Param_CAM.zip下载

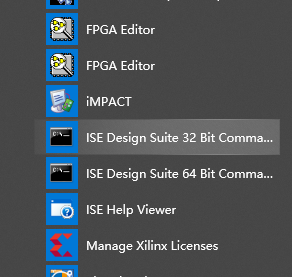

2、解压后采用ISE 命令窗口进行操作

3、进入文件目录然后对IP输入参数

cd /xapp1151_cam_v1_1/implement

xilperl CustomizeWrapper.pl You need to specify several parameters. To choose those options, see follows:***************************************************************

CAM Reference Design Customizer v1.1

******************************************************************************************************************************

Please input the following parameters for the CAM:

***************************************************************Enter the FPGA base architecture to target

Valid options are virtex4, virtex5, virtex6, virtex6l, spartan3, spartan3e, spartan3a, spartan3adsp, aspartan3, aspartan3e, spartan6, kintex7 :

kintex7(我用的是没有kintex7,不知道参考文献中为什么有kintex7,没有那就选virtex6)Input the CAM data width. Valid values are 1-512:

32Input the CAM depth. Valid values are 16-4096:

32Enter the CAM memory type to implement

(Choose SRL-based if you need a Ternary or Enhanced Ternary mode CAM)

0 = SRL-based, 1 = BRAM-based: 0Choose the Ternary Mode setting.

0 = Ternary Mode Off, 1 = Standard Ternary Mode, 2 = Enhanced Ternary Mode: 1Will the CAM be write-able (WE pin)? (If no, CAM will be read-only) (y/n): yUse a MIF file to initialize the memory contents? (y/n): nChoose what type of encoding the MATCH_ADDR port will have.

0 = Binary Encoded, 1 = Single Match Unencoded (one-hot), 2 = Multi-match Unencoded: 1For Binary Encoded or Single Match Unencoded MATCH_ADDR, output lowest address match or highest address match?

0 = Lowest, 1 = Highest: 0Please select the optional features to be implemented:

Simultaneous Read/Write (y/n): yPlease select from the following optional input ports:

Enable (EN) (y/n): nPlease select from the following optional output ports:

Multiple Match Flag (MULTIPLE_MATCH) (y/n): n

Single Match Flag (SINGLE_MATCH) (y/n): n

Read Warning Flag (READ_WARNING) (y/n): nAfter the selections the parameters should be as follows:VHDL parameters were generated as follows:

===============================================

C_FAMILY : string := kintex7;

C_MEM_TYPE : integer := 0;

C_WIDTH : integer := 32;

C_DEPTH : integer := 32;

C_ADDR_TYPE : integer := 1;

C_MATCH_RESOLUTION_TYPE : integer := 0;

C_TERNARY_MODE : integer := 1;

C_HAS_WE : integer := 1;

C_MEM_INIT : integer := 0;

C_HAS_CMP_DIN : integer := 1;

C_REG_OUTPUTS : integer := 0;

C_HAS_EN : integer := 0;

C_HAS_MULTIPLE_MATCH : integer := 0;

C_HAS_SINGLE_MATCH : integer := 0;

C_HAS_READ_WARNING : integer := 0;===============================================4、修改vhdl_xst.scr文件(主要是输出文件名称、iobuf和FPGA型号)

run

-ifmt VHDL

-work_lib cam

-p xc7k325tffg900-2

-write_timing_constraints No

-ifn vhdl_xst.prj

-iobuf No

-max_fanout 100

-ofn ./results/tcam.ngc

-ofmt NGC

-bufg 1

-bus_delimiter ()

-hierarchy_separator /

-case Maintain

-opt_mode Speed

-opt_level 1

-loop_iteration_limit 5000

-use_new_parser yes

5、执行xilperl RunXST.pl(时间比较长)

xilperl RunXST.pl6、生成代码

cd results

netgen -sim -ofmt verilog tcam.ngc修改生成的tcam.v文件,将代码中的模块名cam_wrapper改成tcam。

实际在FPGA中测试是没有问题的(xc7k325t)。

7、仿真测试波形