前言

PGL22G 核心板上配有 1 个 Micron(美光) 的 128MB 的 DDR3 芯片,型号为MT41J128M16HA-125。 DDR 的总线宽度共为 16bit。 DDR3 SDRAM 的最高运行时钟速度可达 400MHz,数据传输频率可达800MHz,故可推算整个系统的带宽可达 10G/b(800M*16bit)。该 DDR3 存储系统直接连接到了 FPGA 的 BANK L1 和 BANK L2的存储器接口上(电压1.5V),如下图所示。

一、实验简介

本实验为后续使用 DDR3 内存的实验做铺垫,通过循环读写 DDR3 内存,了解其工作原理和 DDR3 控制器的写法,由于 DDR3 控制复杂,控制器的编写难度高,这里笔者介绍采用第三方的 DDR3 IP 控制器情况下的应用,是后续音频、视频等需要用到 DDR3 实验的基础。

二、实验原理

DDR SDRAM 全称为 Double Data Rate SDRAM,中文名为“双倍数据流 SDRAM”。DDR SDRAM 在原有的 SDRAM 的基础上改进而来。也正因为如此,DDR 能够凭借着转产成本优势来打败昔日的对手 RDRAM,成为当今的主流。本文只着重讲 DDR 的原理和 DDR SDRAM 相对于传统 SDRAM(又称 SDR SDRAM)的不同。

(一) DDR 的基本原理

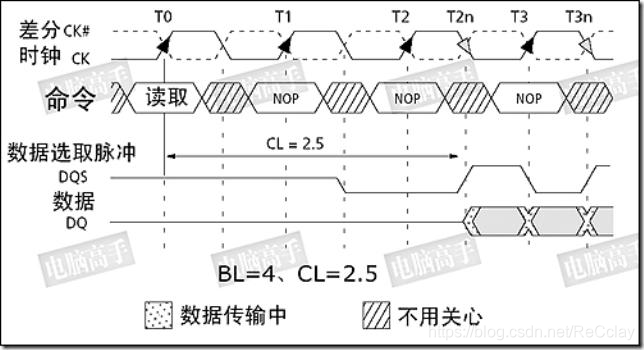

有很多文章都在探讨 DDR 的原理,但似乎也不得要领,甚至还带出一些错误的观点。首先我们看看一张 DDR 正规的时序图。

从中可以发现它多了两个信号: CLK#与 DQS,CLK#与正常 CLK 时钟相位相反,形成差分时钟信号。而数据的传输在 CLK 与 CLK#的交叉点进行,可见在 CLK 的上升与下降沿(此时正好是 CLK#的上升沿)都有数据被触发,从而实现 DDR(双倍速率)。在此,我们可以说通过差分信号达到了 DDR 的目的,甚至讲 CLK#帮助了第二个数据的触发,但这只是对表面现象的简单描述,从严格的定义上讲并不能这么说。之所以能实现 DDR,还要从其内部的改进说起。

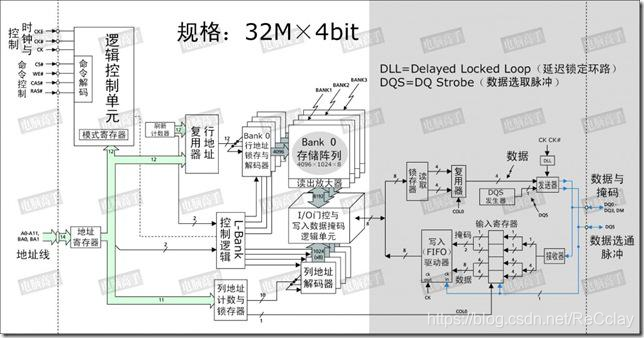

这是一颗 128Mbit 的内存芯片,从图中可以看出来,白色区域内与 SDRAM 的结构基本相同,但请注意灰色区域,这是与 SDRAM 的不同之处。首先就是内部的 L-Bank 规格。SDRAM 中 L-Bank存储单元的容量与芯片位宽相同,但在 DDR SDRAM 中并不是这样,存储单元的容量是芯片位宽的一倍,所以在此不能再套用讲解 SDRAM 时 “芯片位宽=存储单元容量” 的公式了。也因此,真正的行、列地址数量也与同规格 SDRAM 不一样了。

以本芯片为例,在读取时,L-Bank 在内部时钟信号的触发下一次传送 8bit 的数据给读取锁存器,再分成两路 4bit 数据传给复用器,由后者将它们合并为一路 4bit 数据流,然后由发送器在DQS 的控制下在外部时钟上升与下降沿分两次传输 4bit 的数据给北桥。这样,如果时钟频率为100MHz,那么在 I/O 端口处,由于是上下沿触发,那么就是传输频率就是 200MHz。

现在大家基本明白 DDR SDRAM 的工作原理了吧,这种内部存储单元容量(也可以称为芯片内部总线位宽)= 2×芯片位宽(也可称为芯片 I/O 总线位宽)的设计,就是所谓的两位预取(2-bitPrefetch),有的公司则贴切的称之为 2-n Prefetch(n 代表芯片位宽)。

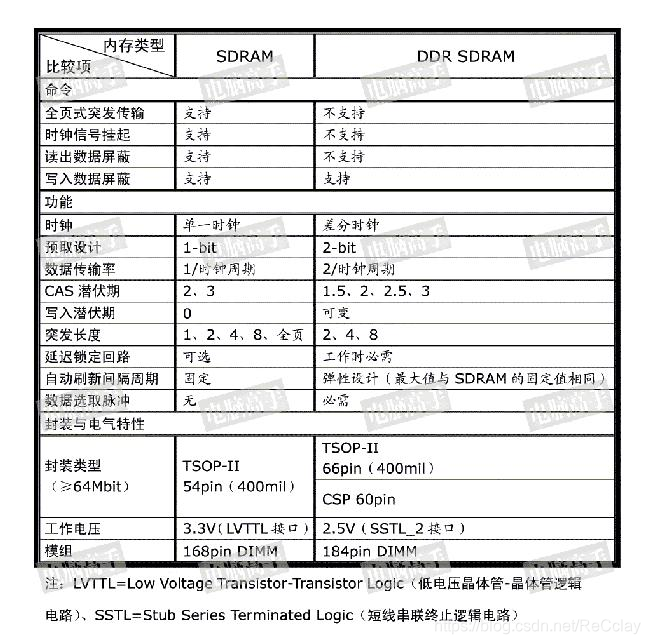

(二) DDR SDRAM 与 SDRAM 的不同

DDR SDRAM 与 SDRAM 的不同主要体现在以下几个方面。

DDR SDRAM 与 SDRAM 一样,在开机时也要进行 MRS,不过由于操作功能的增多,DDRSDRAM 在 MRS 之前还多了一 EMRS 阶段(Extended Mode Register Set,扩展模式寄存器设置),这个扩展模式寄存器控制着 DLL 的有效/禁止、输出驱动强度、QFC 有效/无效等。

由于 EMRS 与 MRS 的操作方法与 SDRAM 的 MRS 大同小异,在此就不再列出具体的模式表了,有兴趣的话可查看相关的 DDR 内存资料。下面我们就着重说说 DDR SDRAM 的新设计与新功能。