�����DZ���¼�� AXI Central Direct Memory Access (CDMA�����ѧϰ�ʼǼ��ο����̷���˵����

���滷��

win10 64bit

vivado 2017.4

modelsim

���ܽ���

IP�ܹ�

ģ��ֽ����

Register Module

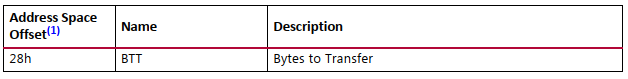

����AXI-CDMA�Ŀ��Ƽ�״̬�Ĵ����� �ӿ� AXI-lite ���Ĵ����б����£�

Scatter/Gather Block

SG����ģ�飬ͨ�� AXI4-SG master�ӿڣ���ȡ����ϵͳ�ڴ��е�CDMA ���ƴ���������������SG �����ṩ�ڲ����������У�ʹ����������Ԥȡ�ʹ����ܺ�CDMA���ݴ���ͬʱ���С������������������£�

DMA Controller

Э��DMģ���������أ�״̬����������״̬���»� register module

DataMover �����������������ݴ��䡣�ṩ4Kbyte��ַ������CDMA������ͻ���Զ���֣���δ��������Զ��Ŷӡ��ṩ�����ַ��д���ݵ� byte-level �ض��빦�ܣ����512bit ����������������

IP�ӿ�

����˵��

ֱ������example���̣�Ȼ�����modelsim���棬������SGģʽ����˵����

����ģ�����£��Լ����ģ����Ϳ��£�

1�� AXI_ATG_LOGIC ����CDMA�Ĵ���������SG Descriptor�� Current Descriptor Pointer��tail Descriptor Pointer

2) AXI_M_SG���� AXI_S_LITE���õ�ָ�룬��SG_BRAM�л�ȡDescriptor list

3��DataMover ����Descriptor list �� U0_read ��ȡ���ݣ�д�뵽 U0_write �С�

4��д��U0_write�����ݣ�ͬʱ��һ��S2MM_DATA_CHECKģ�飬�Ƚ����ݺ�AXI4_FULL�����������Ƿ�һ�£�����pass/fail�źš�

AXI_ATG_LOGIC��CDMA�������£�

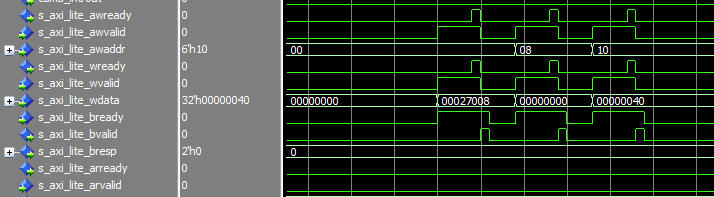

�ֱ����� 0x0, 0x8, 0x10�Ĵ���

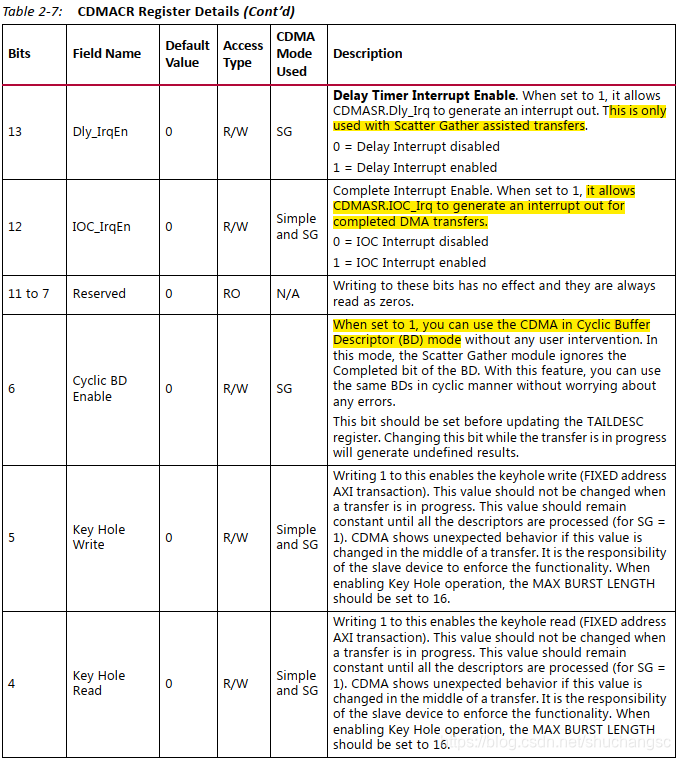

����datasheet�� д�Ĵ���0x0 -> 0x0002_7008

bit[3] = 1 ��ʾ SG mode

bit[12] = 1 ��ʾ IOC_IrqEn

bit[13] = 1��ʾ Dly_IrqEn

bit[14] = 1 ��ʾERR_IrqEn

bit[23:16] = 0x2 ��ʾ IRQThreshold = 0x2

����datasheet�� д�Ĵ���0x8 -> 0x000, ���õ�ǰ������ָ��ָ���ַ0

����datasheet�� д�Ĵ���0x10 -> 0x0000_0040������β������ָ��ָ���ַ0x0000_0040

AXI_ATG_LOGIC д�� 0X10�Ĵ�������SG ENGINE��������SG_BRAM��ȡ discriptor list�� discriptor�Ķ������£�

��ȡ����������������1���£�

����1˵����

0x0 -> NXTDESC_PNTR : 0x0000_0040 , ��һ��������ʼ��ַΪ0x0000_0040

0x4 -> NXTDESC_PNTR_MSB �� 0x0000_0000, ��ַ��λΪ0

0x8 -> SA �� 0x0000_0000, ����Դ��ַΪ0x0000_0000

0xc -> SA_MSB �� 0x0000_0000, ����Դ��λ��ַΪ0x0000_0000

0x10 -> DA �� 0x0000_0000, ���ݰ��˵�Ŀ�ĵ�ַΪ0x0000_0000

0x14 -> DA_MSB �� 0x0000_0000, ���ݰ��˵�Ŀ�ĸ�λ��ַΪ0x0000_0000

0x18 -> CONTROL : 0x0000_0100 , BTT = 0x100 , ��ʾ���� 256byte��

0x1c -> STATUS : 0X0000_0000 , ��ǰdiscriptor ��״̬��bit[31]Ϊ0����ʾδ��ɡ�

����2˵����

����2�ĵ�ַΪ0x0000_0040����axi_lite ���õ� tail discriptor pointer����ʾ���һ��discriptor��

0x0 -> NXTDESC_PNTR : 0x0000_0040 , ��һ��������ʼ��ַΪ0x0000_0040

0x4 -> NXTDESC_PNTR_MSB �� 0x0000_0000, ��ַ��λΪ0

0x8 -> SA �� 0x0000_0000, ����Դ��ַΪ0x0000_0100�� ����Դ��ַΪ0x0000_0100

0xc -> SA_MSB �� 0x0000_0000, ����Դ��λ��ַΪ0x0000_0000

0x10 -> DA �� 0x0000_0000, ���ݰ��˵�Ŀ�ĵ�ַΪ0x0000_0000

0x14 -> DA_MSB �� 0x0000_0000, ���ݰ��˵�Ŀ�ĸ�λ��ַΪ0x0000_0000

0x18 -> CONTROL : 0x0000_0100 , BTT = 0x100 , ��ʾ���� 256byte��

0x1c -> STATUS : 0X0000_0000 , ��ǰdiscriptor ��״̬��bit[31]Ϊ0����ʾδ��ɡ�

���AXI_M_SG ���� SG_BRAM��discriptor����

д0x1c �� 0x5c Ϊ0x8000_0000, �� Transfer Descriptor Status Word (Status �C Offset 1Ch)��bit31д1��complt = 1 ������ɱ�־��

�����

pg034-axi-cdma