简介

- Cortex‐M3 是一个 32 位处理器内核。 内部的数据路径是 32 位的, 寄存器是 32 位的, 存储器接

口也是 32 位的。 CM3 采用了哈佛结构,拥有独立的指令总线和数据总线,可以让取指与数据访问

并行不悖。 这样一来数据访问不再占用指令总线,从而提升了性能。 为实现这个特性, CM3 内部

含有好几条总线接口,每条都为自己的应用场合优化过,并且它们可以并行工作。但是另一方面,

指令总线和数据总线共享同一个存储器空间(一个统一的存储器系统)。换句话说,不是因为有两

条总线,可寻址空间就变成 8GB 了。

比较复杂的应用可能需要更多的存储系统功能,为此 CM3 提供一个可选的 MPU,而且在需要

的情况下也可以使用外部的 cache。 另外在 CM3 中, Both 小端模式和大端模式都是支持的。

CM3 内部还附赠了好多调试组件, 用于在硬件水平上支持调试操作, 如指令断点, 数据观察点

等。另外,为支持更高级的调试,还有其它可选组件,包括指令跟踪和多种类型的调试接口。

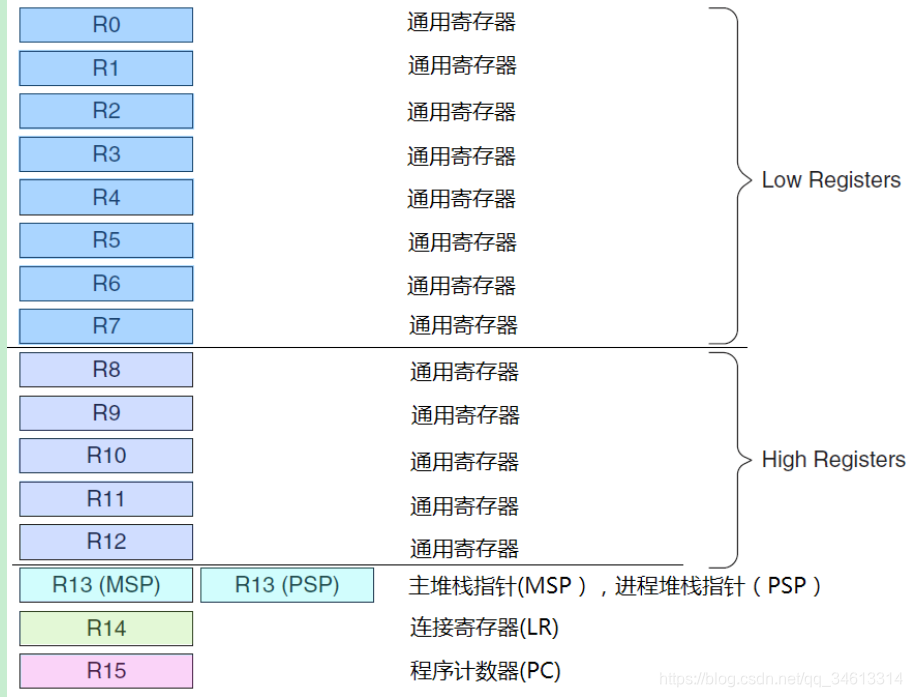

寄存器组

- Cortex‐M3 处理器拥有 R0‐R15 的寄存器组。其中 R13 作为堆栈指针 SP。 SP 有两个,但在同一

时刻只能有一个可以看到,这也就是所谓的“banked”寄存器。

- R0-R12:通用寄存器

- R0‐R12 都是 32 位通用寄存器,用于数据操作。但是注意:绝大多数 16 位 Thumb 指令只能访

问 R0‐R7,而 32 位 Thumb‐2 指令可以访问所有寄存器。 - Banked R13: 两个堆栈指针

Cortex‐M3 拥有两个堆栈指针,然而它们是 banked,因此任一时刻只能使用其中的一个。

z 主堆栈指针(MSP):复位后缺省使用的堆栈指针,用于操作系统内核以及异常处理例程(包括中断服务例程)z 进程堆栈指针(PSP):由用户的应用程序代码使用。堆栈指针的最低两位永远是 0,这意味着堆栈总是 4 字节对齐的。在 ARM 编程领域中,凡是打断程序顺序执行的事件,都被称为异常(exception)。除了外部中断外,当有指令执行了“非法操作”,或者访问被禁的内存区间,因各种错误产生的 fault,以及不可屏蔽中断发生时,都会打断程序的执行,这些情况统称为异常。在不严格的上下文中,异常与中断也可以混用。另外,程序代码也可以主动请求进入异常状态的(常用于系统调用)。 - R14:连接寄存器

当呼叫一个子程序时,由 R14 存储返回地址不像大多数其它处理器, ARM 为了减少访问内存的次数(访问内存的操作往往要 3 个以上指令周期,带 MMU和 cache 的就更加不确定了),把返回地址直接存储在寄存器中。这样足以使很多只有 1 级子程序调用的代码无需访问内存(堆栈内存),从而提高了子程序调用的效率。如果多于 1 级,则需要把前一级的 R14 值压到堆栈里。在 ARM上编程时,应尽量只使用寄存器保存中间结果,迫不得以时才访问内存。在 RISC 处理器中,为了强调访内操作越过

了处理器的界线,并且带来了对性能的不利影响,给它取了一个专业的术语:溅出。 - R15:程序计数寄存器

指向当前的程序地址。如果修改它的值,就能改变程序的执行流(很多高级技巧就在这里面—

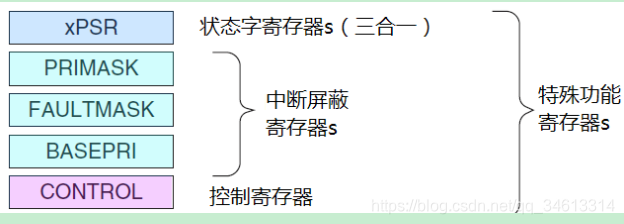

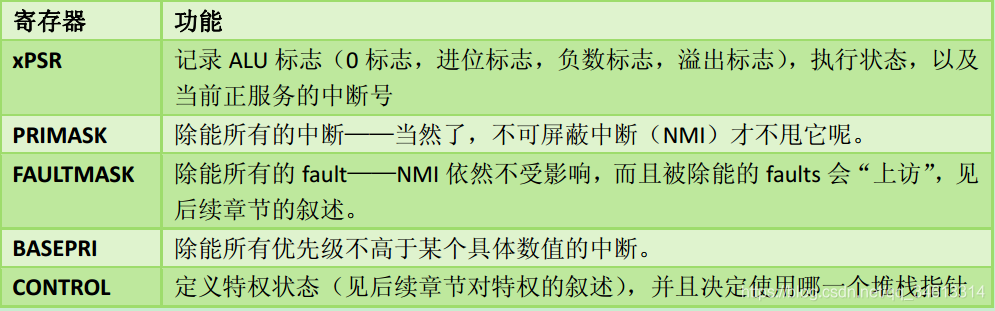

—译注)。 - 特殊功能寄存器

Cortex‐M3 还在内核水平上搭载了若干特殊功能寄存器,包括程序状态字寄存器组(PSRs)中断屏蔽寄存器组(PRIMASK, FAULTMASK, BASEPRI)控制寄存器(CONTROL)

特别注意

- R0~R12在《cortex- m3权威指南》中描述为通用寄存器用来数据操作,但是具体怎么对应并没有明确的指定。

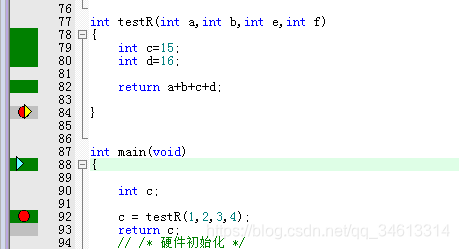

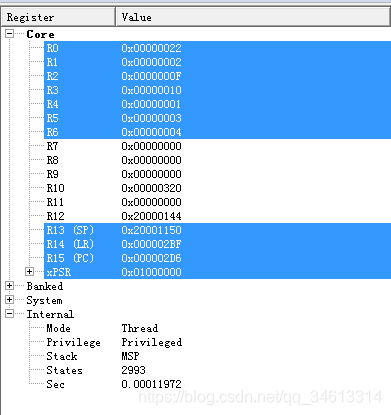

- 在stm32不带操作系统情况下R0~15如图

| 寄存器 | 含义 |

|---|---|

| R0 | testR()返回值 |

| R1 | 形参b的值 |

| R2 | 局部变量c的值 |

| R3 | 局部变量d的值 |

| R4 | 形参a的值 |

| R5 | 形参e的值 |

| R6 | 形参f的值 |

| R13(SP) | 进程堆栈指针PSP |

| R14(LR) | 函数结束后返回的地址 |

| R15(PC) | 当前程序运行的地址 |

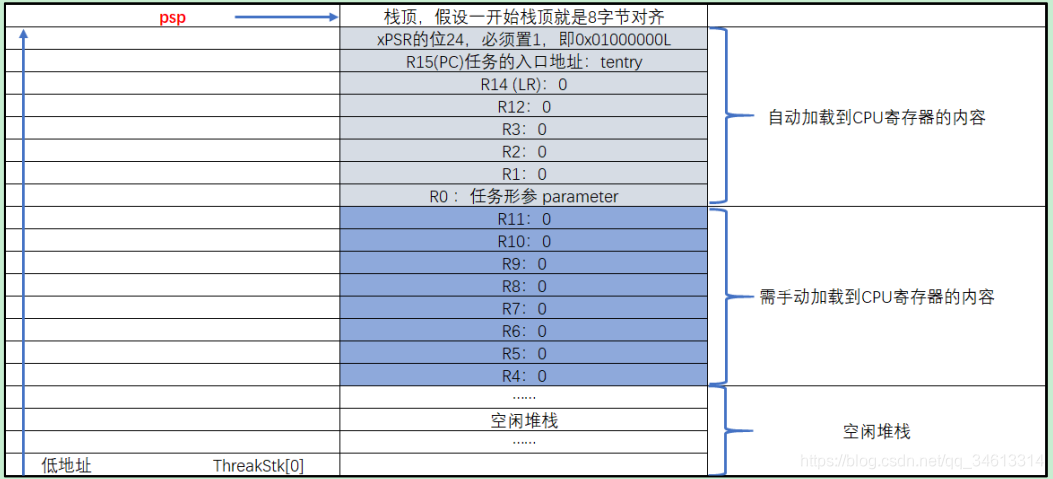

- 在FreeRTOS中,栈中保存的值是如下结构组成的