以下都是自己的理解,如有错误希望大家指正,感激不尽~

目录

Cortex M0

处理器内部的bus matrix

处理器外部的busmatrix

Cortex M3

处理器内部的bus matrix

处理器外部的bus matrix

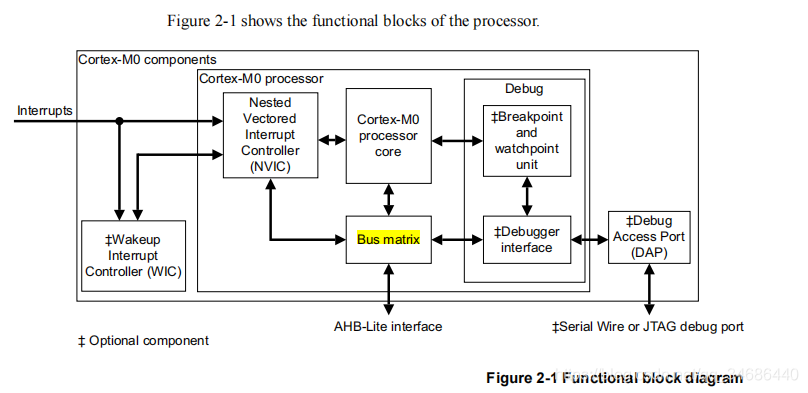

Cortex M0

处理器内部的bus matrix

The processor contains a bus matrix that arbitrates the processor core and optional Debug Access Port (DAP) memory accesses to both the external memory system and to the internal NVIC and debug components.

处理器包含的bus matrix用来仲裁processor core以及DAP的memory access (外部内存以及内部NVIC和调试组件)

处理器外部的busmatrix

首先cortexM0处理器有一个AHB-lite master

如果此时的SoC系统中没有其他的AHBmaster(例如DMA)

此时就无须使用Bus matrix。(因为不需要对总线的使用权进行总裁,整个系统只有一个AHB-lite master)

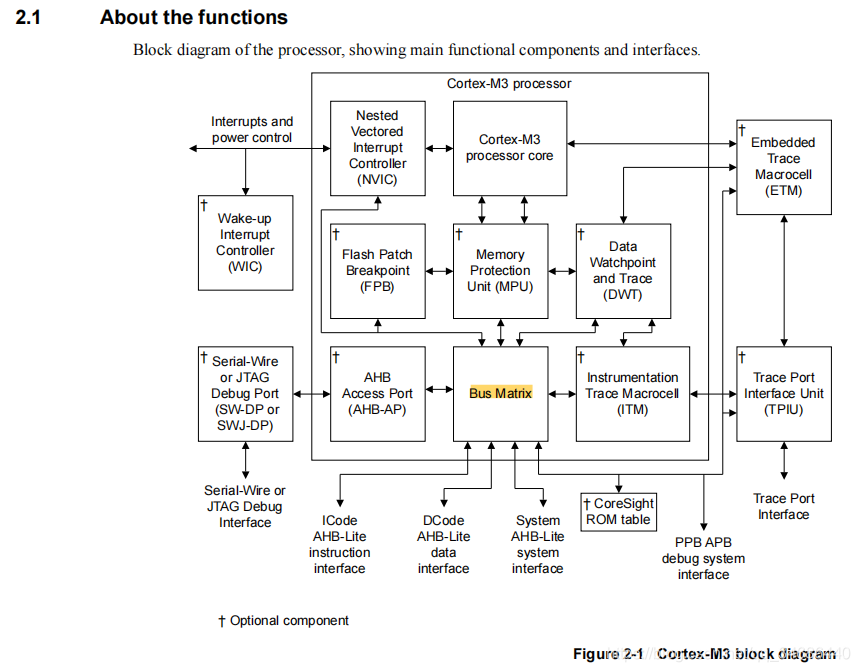

Cortex M3

处理器内部的bus matrix

The processor contains a bus matrix that arbitrates accesses to both the external memory system and to the internal System Control Space (SCS) and debug components, supports ARMv7 unaligned accesses, and performs all accesses as single, unaligned accesses.

处理器外部的bus matrix

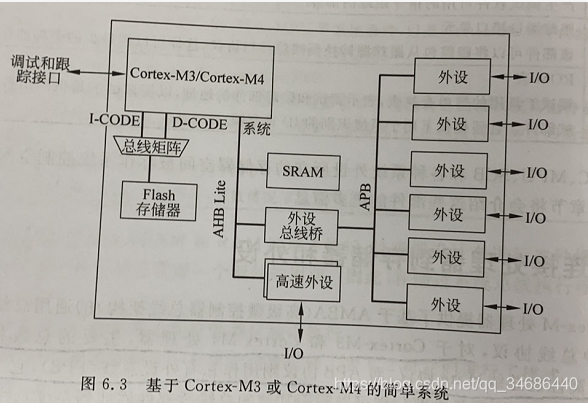

在简单的微处理器设计中,程序存储器一般会被连接到I-CODE和D-CODE总线,而SRAM和外设会被连接到系统总线。

一种简单的设计如图所示:

程序存储器的访问具有两个总线接口I-CODE和D-CODE总线,在简单的设计中可以利用ARM提供的总线复用部件将这两个总线合并。

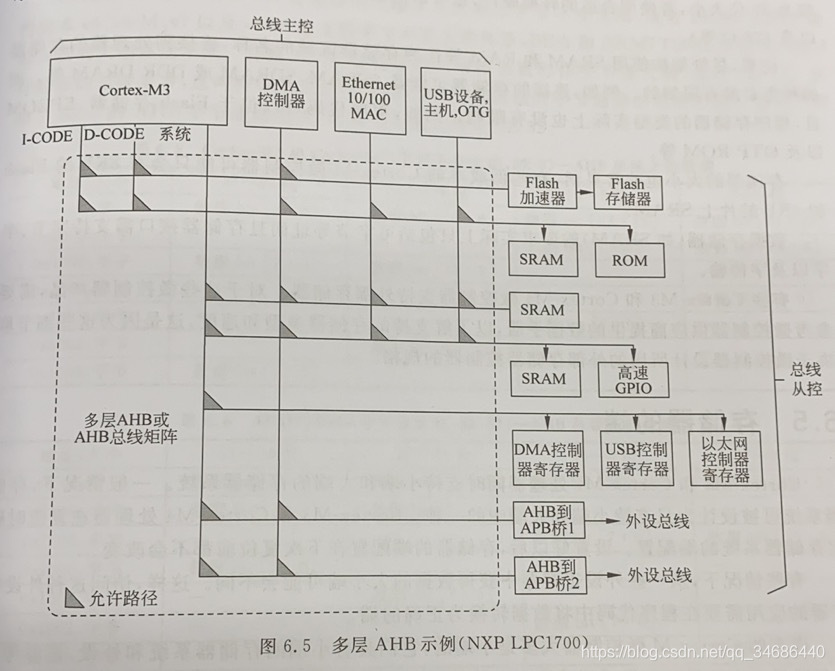

在许多的CortexM3处理器产品中,还可以在内部总线中发现多个总线主控设备,如DMA,以太网,USB控制器,这些产品的文档一般会出现总线举证或者多层AHB等说法

这意味着对于内部总线系统中的AHB连接,多个总线主设备可以同时执行对不同存储器或者外设的访问。

如果两个主设备同时访问同一个总线从部件,总线矩阵将会总裁,让更高优先级的主设备先通过