- 新建rtl工程

打开vivado,左侧功能区选择Quick Start-->Create Project;

选择RTL Project

选择当前的器件:

- 搭建硬件平台

在左侧功能区中选择 IP INTEGRATOR-->CreateBlockDesign

右侧窗口出现一个Diagram窗口

屏幕剪辑的捕获时间: 2018/1/12, 9:54

![]()

点击 下拉列表中选择Microblaze,添加到设计区,然后双击可以配置microblaze的参数,我们用默认参数;

搭建外围器件,在设计区上面会出现一个Run Block automation 选项,点击可以自动连接需要的外围器件,配置microblaze外围设置:

搭建的最基本的硬件平台如下:

现在增加串口模块,AXI uartlite,点击Run Connection Automation 自动连接,如下:

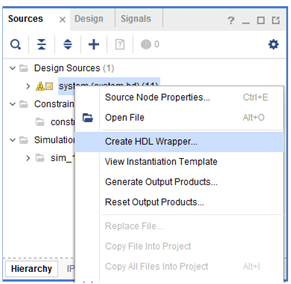

对系统进行封装(wrapper),右击Design Sources下system,选择Create HDL Warpper

这时候会提示一个错误:Port/Pin property POLARITY does not match between /clk_wiz_1/reset(ACTIVE_HIGH) and /reset_rtl_0(ACTIVE_LOW);

修改clk_wiz_1模块中的reset中高有效改成低有效;

- 注意事项:

・AXI内部连接器(AXI Interconnect)可以连接多个Master设备和多个Slave设备,各个设备可以用不同的时钟进行通信,前提是ARESETN和ACLK为当前设置用时钟和复位;

- 硬件平台改变:

重新导入硬件平台,如果在SDK中多了一个hw_platform,则需要重新建立依赖新平台的一个bsp,然后改变程序的BSP设置,注意不能先把旧bsp删除;修改好以后才能删除;