上篇博文讲了输入延迟约束( Input Delay Constraints):输入延迟约束(Constraining Input Delay)

这篇博文讲解具体的实例,通过实例去学习是最有效果的。

实例1

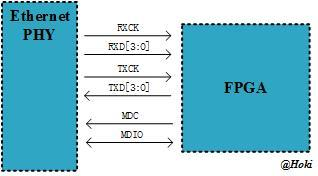

如图1所示系统,以太网PHY芯片与FPGA相连,分为三组接口:

RX接口:时钟RXCK和数据RXD;

TX接口:时钟TXCK和数据TXD;

MII管理接口:时钟MDC和数据MDIO。

(图1)

其中RX接口属于源同步输入接口,以下就以RX接口为例讲解一下约束input delay:

Clock Constraints:

首先约束时钟,如图2所示为PHY(DP83849ID)在100Mb/s模式下的时序图,时钟和数据为Center Aligned关系,因此时钟在FPGA中无需再移相,可直接使用RXCK采集数据,时钟约束如下:

create_clock –name RXCK –period 40 –waveform {0 20} [get_ports {RXCK}]

(图2)

???????Input Delay Value

根据上节中源同步输入计算Input Delay的公式:

max_input_delay = Tbd_max + Tco_max - Tcd_min

min_input_delay = Tbd_min + Tco_min - Tcd_max

Tbd为数据线RXD在板上的延时,也就是信号在电路板上的传播时间。查找了网上的一些资料:

“信号速度还与不同材料的介电常数相关,具体计算公式是 V=C/Er0.5 ,其中Er是信号线周围材料的相对介电常数。我们常见的PCB材料Fr4的介电常数在4.2-4.5左右,为了计算方便我们取4。带入公式可以算出,Fr4材料制作的PCB板上面信号的传输速度是光速的二分之一。光速大约等于12inch/ns,计算得出Fr4板上信号速度大约是6inch/ns。换算成延时,也就是166ps/inch。这就是我们经常说的PCB板上信号延时大约是166ps/inch。”

在此例中,通过PCB设计软件计算得到RXD[3:0]的走线长度,分别是LRXD[3]=426mil,LRXD[2]=451mil,LRXD[1]=502mil,LRXD[0]=406mil,因此可以计算得到:

Tbd_max = 502mil * 166ps/inch = 0.083332ns

Tbd_min = 406mil * 166ps/inch = 0.067396ns

Tcd为时钟线RXCK在板上的延时,走线长度LRXCK=399mil,因此可以计算得到:

Tcd_max=Tcd_min=399mil * 166ps/inch = 0.066234ns

Tco为RX接口clock_to_output时间,如图2中,等于T2.5.2时间参数,因此可得到:

Tco_max = 30ns

Tco_min = 10ns

综上:

max_input_delay = Tbd_max + Tco_max - Tcd_min = 0.083332ns + 30ns - 0.066234ns = 30.017098ns

min_input_delay = Tbd_min + Tco_min - Tcd_max = 0.067396ns + 10ns - 0.066234ns = 10.001162ns

???????Constraints

很显然,RX接口为SDR,时钟约束和input delay值的计算后,可以对input delay进行约束,命令如下:

set_input_delay -clock[get_clocks RXCK] -max 30.017098[get_ports {RXD[3] RXD[2] RXD[1] RXD[0]}]

set_input_delay -clock[get_clocks RXCK] -min 10.001162[get_ports {RXD[3] RXD[2] RXD[1] RXD[0]}]

在Vivado的GUI界面中也可以进行约束,设计经过综合实现后,打开编辑约束文件,如图3所示

(图3)

选择Set Input Delay,在右侧双击,可弹出Input Delay设置窗口,如图4所示

(图4)

在弹出的Input Delay窗口中设置参数,如图5所示,Input Delay约束完成。

(图5)

实例2

在实例1中,如图1所示,对RX接口进行了约束。另外MII管理接口,其中MDIO是双向数据接口,肯定需要input delay的约束

(图1)

最初以为MII接口属于源同步输入,但是仔细查看后发现不对劲儿,时钟MDC并不是由PHY提供的,而是FPGA输出给PHY的,这与源同步接口的定义矛盾,源同步需要时钟和数据来自同一个源。因此只能划分到系统同步输入范畴了,仔细一想还是能说得通的,系统同步中只要求source clock和destination clock来自同一个时钟网络即可,不管是在FPGA外部还是内部,如图2所示,

(图2)

系统同步输入的input delay value计算公式如下:

max input delay = Tclkd_ext_max + Tco_max + Tbd_max – Tclkd_int_min

min input delay = Tclkd_ext_min + Tco_min + Tbd_min – Tclkd_int_max

此例的情况,时钟源到FPGA输入端口的延时Tclkd_int等于0,时钟源到外部芯片的延时为TCD,因此得到变化后的公式如下:

max input delay = TCD_max + TCO_max + TBD_max

min input delay = TCD_min + TCO_min + TBD_min

各时间参数的计算如下:

TCD :时钟线MDC在板上的长度LMDC=489mil,TCD_max= TCD_min=489mil*166ps/inch= 0.081174ns

TBD:数据线MDIO在板上的长度LMDIO=634mil,TBD_max= TBD_min=634mil*166ps/inch= 0.105244ns

TCO: 参考PHY(DP83849ID)的手册,如图3所示,TCO等于时间参数T2.3.1,得到TCO_max=30ns,TCO_min=0ns。

图3

得到input delay值如下:

Max_input_delay = TCD_max + TCO_max + TBD_max

=0.081174ns+30ns+0.105244ns=30.186418ns

min input delay = TCD_min + TCO_min + TBD_min

=0.081174ns+0ns+0.105244ns=0.186418ns

综上,MII管理接口的约束如下:

create_clock –name MDC –period 400 –waveform {0 200} [get_ports {MDC}]

set_input_delay -clock[get_clocks MDC] -max 30.186418[get_ports {MDIO}]

set_input_delay -clock[get_clocks MDC] -min 0.186418[get_ports {MDIO}]

在Vivado中的约束如图4,5所示:

图4、5、6