目录

背景

正文

测试

放置在Module前

放置在变量声明前

附加测试

放置在某个变量声明前

放置在Module前

相关链接

背景

在做一些FPGA算法的时候,我们不可避免的使用到大量的算术运算,例如复数乘法器,乘法器,加法器,减法器,还有乘加,乘减,乘累加等等。

我们都知道FPGA底层有专用的DSP48E资源,也有大量的逻辑资源,放着专用资源DSP48E不用,或者只用DSP48E,都不是好的选择,要看情况使用,这个情况需要考虑资源数量,实现性能等。

RTL级设计很方便,可以直接用算术运算符去实现加减乘、取余、取整等运算,但这种方便的同时,会带来很多不确定性。我们在Vivado设计中,需要考虑到资源的使用是使用dsp资源呢?还是使用fabric资源(底层逻辑资源)?

把命运交给综合工具推断?还是自己掌握?凡事预则立不预则废,我们来看看如何使用标题中的综合属性use_dsp48?

注意:如果使用IP核去生成乘法器,加法器,减法器等等,可以直接在定制时刻选择,另当别论。

正文

use_dsp48综合属性提示综合工具如何处理算术运算的实现结构;

在默认的情况下,如下的算术类型结构会综合成DSP48E资源;

Mult

Mult-add&Mult-sub

Mult-accumulate

而adders,subtracters,与accumulators在默认情况下会使用fabric资源实现;

fpga的专用资源dsp48具有性能高的优点,如果我们想节省下来一些LUT逻辑资源,可以通过这样的综合属性来提示综合工具使用dsp48资源而同时释放一些LUT逻辑资源。

该属性会覆盖默认行为并强制将这些结构强制转换为DSP48块,并将其置于RTL中signals,architectures和components,entities和module上,具有以下优先级:

Signals

Architectures and components

Modules and entities

此属性的可接受值为“yes”和“no”。

测试

我们使用24位加法器来实际测试这个综合属性的使用:

如果不添加任何综合限制,默认应该使用LUT资源,测试如下:

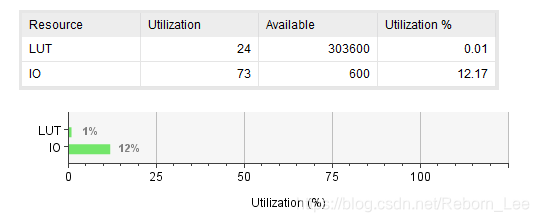

如果没有添加这句综合属性,那么综合使用资源情况为:

module adder24(input [23:0] a,input [23:0] b,output [24:0] sum);assign sum = a + b;endmodule

可见,和预期一致,使用的是FPGA的逻辑资源,并且使用了24个LUT资源。

如果使用综合属性use_dsp48呢?测试如下:

放置在Module前

首先必须说一下USE_DSP48,这句话可以放在模块的前面,也可以放在reg声明的前面,如下:

(*use_dsp48="yes"*)

module adder24(input [23:0] a,input [23:0] b,output [24:0] sum);assign sum = a + b;endmodule

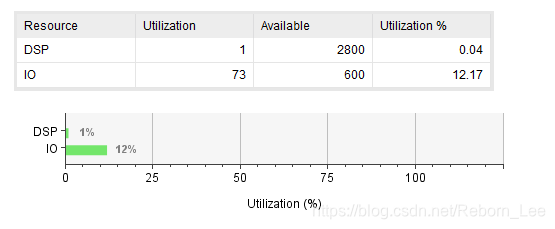

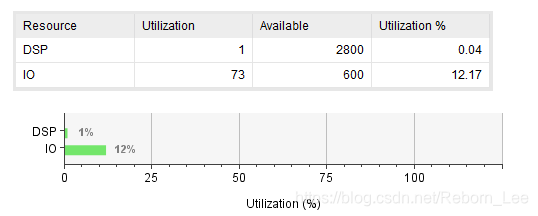

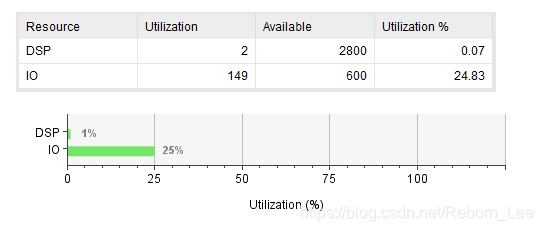

可见,仅仅使用了一个DSP48E即可,同时对于我们的FPGA(这里使用的是V7进行实验),DSP48资源很多,如果不用,即获得不了高性能,也造成了资源的闲置。

放置在变量声明前

放到变量声明前面,如下:

module adder24(input [23:0] a,input [23:0] b,output [24:0] sum);

(*use_dsp48="yes"*) wire [24:0] sum;assign sum = a + b;endmodule

可见,与放在Module前面综合结果一致;

但是,这只是针对加法器这么一个简单的模块,如果你的模块中还有其它更复杂的逻辑,那么建议使用第二种方法,只对某些特定的逻辑使用DSP单元。

附加测试

放置在某个变量声明前

最后两种情况,由于模块内部运算只有一个,貌似不具有说服力,因此,改成如下代码进行测试:

module adder24(input [23:0] a,input [23:0] b,input [24:0] c,input [24:0] d,output [25:0] sum_cd,output [24:0] sum_ab);(*use_dsp48="yes"*) wire [24:0] sum_ab;wire [25:0] sum_cd;assign sum_ab = a + b;assign sum_cd = c + d;endmodule

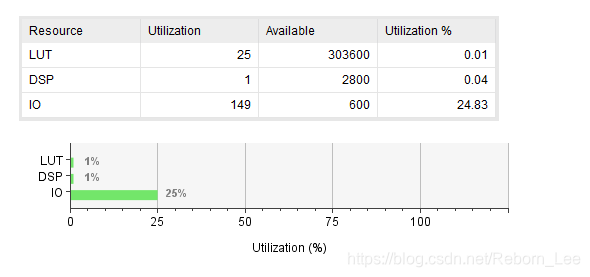

可见,和预期一致,既使用了LUT资源又使用了DSP资源,原因就是在某个变量之前加了综合属性use_dsp48;

放置在Module前

(*use_dsp48="yes"*) module adder24(input [23:0] a,input [23:0] b,input [24:0] c,input [24:0] d,output [25:0] sum_cd,output [24:0] sum_ab);wire [24:0] sum_ab;wire [25:0] sum_cd;assign sum_ab = a + b;assign sum_cd = c + d;endmodule

可见,仅仅使用了DSP资源。

综上,use_dsp48的使用位置有两种,一种是在Module前面使用,这样module内部所有的算术运算均使用dsp资源,另一种是在变量的声明前使用,这样只对部分算术运算使用dsp资源。两种方式的使用,可根据实际需要决定。

相关链接

Vivado入门与提高

综合属性------parallel_case /tanslate_off/tanslate_on/use_dsp48