目录

dont_touch

fsm_encoding

dont_touch

可以参考:

Vivado中如何避免信号被优化掉?

fsm_encoding

我们在RTL设计中,在状态机的设计中,会给状态变量一些状态编码,在parameter中给出,

例如:

这是二进制编码:

这是格雷码:

这是独热码:

但是在RTL中这么设计真的有用吗?或者说综合工具就会给综合成这种编码方式?

光说不练假把式,我们来实际看看综合情况:

拿这篇博客中:【 FPGA 】序列检测器的Moore状态机实现中的序列检测器为例:

设计一个序列检测器,检测序列1101,检测到输出1,否则输出0.

编码方式:二进制编码

`timescale 1ns / 1ps

//

// Company:

// Engineer: 李锐博恩

// Create Date: 2019/01/04 11:16:29

// Module Name: seq_det_moore

//编码方式:二进制编码

//module seq_det_moore(input clk,input reset,input din,output reg dout);//状态声明localparam [2:0]s0 = 3'b000,s1 = 3'b001,s2 = 3'b010,s3 = 3'b011,s4 = 3'b100;reg [2:0] current_state,next_state;always @(posedge clk, posedge reset)beginif(reset)current_state <= s0;elsecurrent_state <= next_state;endalways @ *begincase(current_state)s0:if(din == 1'b1) next_state = s1;else next_state = s0;s1:if(din == 1'b1) next_state = s2;else next_state = s0;s2:if(din == 1'b0) next_state = s3;else next_state = s2;s3:if(din == 1'b1) next_state = s4;else next_state = s0;s4:if(din == 1'b1) next_state = s1;else next_state = s0;default: next_state = s0;endcaseendalways @*beginif(current_state == s4) dout = 1;else dout = 0;endendmodule打开log,可以看到状态机的编码方式为:

如果在RTL设计中采用独热码设计:

`timescale 1ns / 1ps

//

// Company:

// Engineer: 李锐博恩

// Create Date: 2019/10/23 16:14:30

// Module Name: seq_det_moore

//编码方式:独热码编码

//module seq_detect(input clk,input reset,input din,output reg dout);//状态声明localparam [4:0]s0 = 5'b00001,s1 = 5'b00010,s2 = 5'b00100,s3 = 5'b01000,s4 = 5'b10000;reg [4:0] current_state,next_state;always @(posedge clk, posedge reset)beginif(reset)current_state <= s0;elsecurrent_state <= next_state;endalways @ *begincase(current_state)s0:if(din == 1'b1) next_state = s1;else next_state = s0;s1:if(din == 1'b1) next_state = s2;else next_state = s0;s2:if(din == 1'b0) next_state = s3;else next_state = s2;s3:if(din == 1'b1) next_state = s4;else next_state = s0;s4:if(din == 1'b1) next_state = s1;else next_state = s0;default: next_state = s0;endcaseendalways @*beginif(current_state == s4) dout = 1;else dout = 0;endendmodule

特么还真是独热码!

如果我们加上这条综合属性呢:(在状态变量之前加上此综合属性)

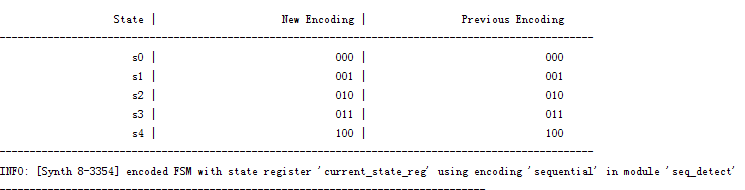

(*fsm_encoding = "sequential"*) reg [4:0] current_state,next_state;

![]()

可见,即使你代码里面用了独热码,但是加了这条综合属性后,最终综合工具会断定状态机的编码方式为综合属性指定的编码方式。

所以,在RTL代码中直接用十进制来设计即可,至于综合成什么样子的编码,通过综合属性来指定即可。

这句话告诉你如何查看FSM的信息:

The Vivado synthesis flags INFO messages in the log file, giving information about Finite State Machine (FSM) components and their encoding. The following are example messages: INFO: [Synth 8-802] inferred FSM for state register 'state_reg' in module 'fsm_test' INFO: [Synth 8-3354] encoded FSM with state register 'state_reg' using encoding 'sequential' in module 'fsm_test'

简而言之,在log文件中查看即可。

参考:UG901